# CREST

ARCHITECTURAL DEVELOPMENTS TOWARDS

# **CRESTA White Paper**

Authors: Jeremy Nowell (UEDIN), Michèle Weiland (UEDIN), Alistair Hart (CRAY UK), Jan Westerholm (ABO), Artur Signell (ABO), Berk Hess (KTH), Erik Lindahl (KTH), George Mozdzynski (ECMWF), Stefano Markidis (KTH)

Editors: Mark Parsons, Lorna Smith, Andy McDonald (UEDIN)

Collaborative Research Into Exascale Systemware, Tools and Applications (CRESTA) ICT-2011.9.13 Exascale computing, software and simulation

# FOREWORD

BY **DR MICHÈLE WEILAND**, FROM EPCC, THE SUPERCOMPUTING CENTRE AT THE UNIVERSITY OF EDINBURGH, UK, AND "UNDERPINNING AND CROSS-CUTTING TECHNOLOGIES" WORK PACKAGE LEADER IN CRESTA.

Developing a computer system that can deliver sustained Exaflop performance is an extremely difficult challenge for the HPC and scientific community. In addition to developing hardware that can compute an Exaflop within a feasible power budget, scientific applications need to be able to exploit the performance that such a system can offer.

The applications can only achieve this type of performance if they are supported by a complete stack of systemware, programming models, compilers, libraries and tools. However developing this stack, not to mention the applications, takes many man-years of effort. In order to be able to direct such efforts efficiently, it is important to try and predict what the architecture of an Exascale system may look like. Although it is obviously not possible to predict future developments with 100% accuracy, estimates that are based on the analysis of past trends in HPC system architecture development in conjunction with the trends in the current market will provide some guidance.

In this white paper, we give our own analysis of the architectural developments towards Exascale systems and discuss the implications for the CRESTA co-design applications.

# ABOUT CREST

BY **PROFESSOR MARK PARSONS**, COORDINATOR OF THE CRESTA PROJECT AND EXECUTIVE DIRECTOR AT EPCC, THE UNIVERSITY OF EDINBURGH.

The Collaborative Research into Exascale, Systemware Tools and Applications (CRESTA) project is focused on the software challenges of Exascale computing, making it a unique project. While a number of projects worldwide are studying hardware aspects of the race to perform 10<sup>18</sup> calculations per second, no other project is focusing on the Exascale software stack in the way that we are. By limiting our work to a small set of representative applications we hope to develop key insights into the necessary changes to applications and system software required to compute at this scale.

When studying how to compute at the Exascale it is very easy to slip into a comfort zone where incremental improvements to applications eventually develop the necessary performance. In CRESTA, we recognise that incremental improvements are simply not enough and we need to look at disruptive changes to the HPC software stack from the operating system, through tools and libraries to the applications themselves. From the mid-1990s to the end of the last decade, HPC systems have remained remarkably similar (with performance increases being delivered largely through the increase in microprocessor speeds). Today, at the petascale, we are already in an era of massive parallelism with many systems containing several hundred thousand cores. At the Exascale, HPC systems may have hundreds of millions of cores. We simply don't know how to compute with such a high level of parallelism.

CRESTA is studying these issues and identifying a huge range of challenges. With the first Exascale system expected in the early 2020s, we need to prepare now for the software challenges we face which, we believe, greatly outnumber the corresponding hardware challenges. It is a very exciting time to be involved in such a project.

# CREST WHITE PAPERS

BY **DR LORNA SMITH**, FROM EPCC, THE SUPERCOMPUTING CENTRE AT THE UNIVERSITY OF EDINBURGH, UK, AND THE CRESTA PROJECT MANAGER.

CRESTA's remit involves preparing applications and software for future Exascale platforms. Beyond this, there is an extensive programme of research activities looking to develop new techniques and algorithms to exploit future Exascale systems. This series of white papers showcases this work and aims to disseminate this to the wider HPC community.

The first of our white papers formed part of our research into the development environment and looked at the state-of-the-art in compilers, programming models and performance and analysis tools. This, and many of the other aspects of CRESTA, are informed by a programme of work looking at underpinning technologies. Underpinning all of our work is an understanding of the current trends in architectures and how they will influence future Exascale platforms – an understanding generated from a set of technology update reports. These reports form the basis of this second white paper and we hope this paper will help inform your research as much as it has CRESTA's.

# CONTENTS

| 1 | EXECUTIVE SUMMARY                                             | 1  |

|---|---------------------------------------------------------------|----|

| 2 | INTRODUCTION                                                  | 2  |

|   | 2.1 GLOSSARY OF ACRONYMS                                      | 3  |

| 3 | THE HIGH PERFORMANCE COMPUTING MARKETS                        | 4  |

| 4 | CURRENT TECHNOLOGY TRENDS                                     | 9  |

|   | 4.1 UNDERLYING BASIC TECHNOLOGIES                             | 9  |

|   | 4.1.1 Semiconductor Technology                                | 9  |

|   | 4.1.2 Communication                                           | 10 |

|   | 4.2 SYSTEM BUILDING BLOCKS                                    | 11 |

|   | 4.2.1 Processors                                              | 11 |

|   | 4.2.1.1 Intel                                                 | 12 |

|   | 4.2.1.2 AMD                                                   | 13 |

|   | 4.2.1.3 IBM                                                   | 14 |

|   | 4.2.1.4 ARM                                                   | 14 |

|   | 4.2.1.5 Nvidia                                                | 15 |

|   | 4.2.1.6 Processor licensing                                   | 15 |

|   | 4.2.2 Memory                                                  | 15 |

|   | 4.2.3 interconnect<br>4.2.4 Software                          | 16 |

|   | 4.2.4 Software                                                | 16 |

| 5 | SYSTEM ARCHITECTURE TRENDS                                    | 18 |

|   | 5.1 DEFINING INFLUENCES                                       | 18 |

|   | 5.2 TRENDS IN THE TOP500 LIST                                 | 19 |

|   | 5.2.1 Processors                                              | 19 |

|   | 5.2.2 Accelerators                                            | 19 |

|   | 5.2.3 System Architectures                                    | 19 |

|   | 5.2.4 Interconnect                                            | 20 |

|   | 5.2.5 Conclusions from ToP500                                 | 20 |

|   | 5.3 MORE RECENT FACTORS                                       | 21 |

|   | 5.4 FUTURE HPC SYSTEMS                                        | 22 |

| 6 | CASE STUDY: TECHNOLOGY TRENDS AND THE CRAY XC30 SUPERCOMPUTER | 23 |

|   | 6.1 PROCESSOR TRENDS                                          | 23 |

|   | 6.2 INTERCONNECT TRENDS                                       | 24 |

|   | 6.3 SYSTEM INTEGRATION AND SOFTWARE                           | 25 |

|   | 6.4 SUMMARY                                                   | 26 |

| 7 | APPLICATION IMPACT                                            | 27 |

|   | 7.1 ELMFIRE                                                   | 27 |

|   | 7.1.1 Introduction                                            | 27 |

|   | 7.1.2 Impact of Current Architectures                         | 27 |

|   | 7.1.3 Impact of Future Architectures                          | 27 |

|   | 7.1.4 Requirements on Future Architectures                    | 27 |

| 7.2 GROM | MACS                                 | 28 |

|----------|--------------------------------------|----|

| 7.2.1    | Impact of Future Architectures       | 28 |

| 7.2.2    | Impact of Current Architectures      | 28 |

| 7.2.3    | Impact of Future Architectures       | 28 |

| 7.2.4    | Requirements on Future Architectures | 29 |

| 7.3 IFS  |                                      | 29 |

| 7.3.1    | Introduction                         | 29 |

| 7.3.2    | Impact of Current Architectures      | 29 |

| 7.3.3    | Impact of Future Architectures       | 29 |

| 7.3.4    | Requirements on Future Architectures | 30 |

| 7.4 Nek5 | 000                                  | 30 |

| 7.4.1    | Introduction                         | 30 |

| 7.4.2    | Impact of Current Architectures      | 30 |

| 7.4.3    | Impact of Future Architectures       | 31 |

| 7.4.4    | Requirements on Future Architectures | 31 |

| 7.5 SUMN | MARY OF APPLICATION IMPACT           | 31 |

| CONCLU   | SIONS                                | 32 |

| REFERE   | NCES                                 | 33 |

# INDEX OF FIGURES

8 9

| Figure 1: Worldwide Tablet and PC Forecast. Taken from [3]                                                                                          | 4          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| <b>Figure 2:</b> Evolution of the geographical share of the performance in the TOP500 list over the last ten years (November 2003 to November 2013) | 6          |

| Figure 3: Geographical share of the November 2013 TOP500 list                                                                                       | 7          |

| Figure 4: Share of the November 2013 TOP500 list by country                                                                                         | 8          |

| Figure 5: CMOS production capabilities. From [8]                                                                                                    | 10         |

| Figure 6: Market share of semiconductor manufacturers. Taken from [10]                                                                              | 11         |

| Figure 7: The Intel tick-tock model, taken from [11]                                                                                                | 12         |

| Figure 8: AMD Server Roadmap. Taken from [21]                                                                                                       | 13         |

| Figure 9: The evolution of AMD's memory architecture. Taken from [22]                                                                               | 14         |

| Figure 10: Memory layout on AMD's HSA processors. Taken from [22]                                                                                   | 14         |

| Figure 11: Market share of accelerators in November 2013 TOP500 list, taken from [                                                                  | 4] 20      |

| Figure 12: Evolution of the energy efficiency of the top 5 systems from the Green500 since November 2007                                            | 0 list, 21 |

# INDEX OF TABLES

# 1 EXECUTIVE SUMMARY

High Performance Computing (HPC) is a growing market. It is increasingly seen to be vital for a nation's scientific and industrial competitiveness. More and more countries provide centralised funding for research into HPC; China, for instance, has seen significant growth over the last few years, and as a result the fastest HPC system in the world (at the time of writing) is in China. The quest to make a supercomputer with Exascale performance requires significant technological advances, particularly given the limited power budget that such a machine will have to operate within. Such advances may come from the wider computing market, where the enormous growth in mobile computing is driving research into power efficient technology, or from research funding specifically for HPC.

In order to understand what an Exascale machine may look like it is informative to study past and current trends in relevant technology. Underlying trends in both semiconductor and communication technology drive developments across the computing landscape. These in turn lead to advances in system building blocks: processors, memory, interconnect and software. By looking at roadmaps from technology providers some trends become clear: firstly the growth in heterogeneous systems involving different types of processors, such as a traditional general purpose CPUs and GPUs; secondly, the trend towards integration of components in System-on-Chip (SoC) silicon; and finally, the growth in licensing intellectual property, such a processor designs, to other manufacturers. Several factors are important when considering HPC system architecture trends. These include performance, programmability and usability, power usage and efficiency, cost of procurement and cost of ownership. The TOP500 list provides 20 years worth of data to analyse architecture trends. There has been a general move towards using commodity components over custom technology, however this has resulted in an emphasis on floating-point performance at the cost of improvements in memory, interconnect and I/O subsystems. One example that illustrates this trend followed by HPC systems over the past couple of decades is the development of Cray's XC30 system, which is detailed in this white paper.

An Exascale machine is only useful if it has applications capable of using it. The CRESTA co-design applications provide an excellent source of information on the impact of architecture trends on application performance and design. Heterogeneous systems are seen as inevitable when pushing towards the Exascale; however they have to be easier for application developers to exploit. This will be achieved by providing better integration, particularly through a single addressable memory space, and more importantly through the provision of standard, well-supported programming models and languages. Highly parallel systems with millions of processors (and potentially billions of parallel threads) will need a matching high performance interconnect to allow the system to be fully exploited by applications. Although the wider market may provide advances in power efficient processor technology, funding for HPC specific research into interconnects, programming models, application development and software engineering for massive parallelism will be required.

# 2 INTRODUCTION

The principle of co-design of both Exascale hardware and scientific applications lies at the heart of CRESTA; this white paper aims to link trends in HPC architectures with the potential impact on the applications.

Key to the development of future Exascale machines are both various underlying development trends and the HPC marketplace. We therefore give a brief overview of the HPC market as it currently stands in Section 3. The first of these trends is the development of basic underlying technologies, used throughout the computer industry. Next are market trends, both within the entire computing industry as well as those specific to the HPC segment of the market. These are described in Section 4.2 in conjunction with the technologies. Taking a wider view, what might an Exascale machine of the future look like from an architectural viewpoint? Predicting this is very difficult and it is imperative to take into account the development trends already mentioned earlier along with HPC specific developments. This is done in Section 5. A case study in Section 6 looks at the development of Cray's latest system, the XC30.

Application development and design is key to achieving Exascale performance on future machines, therefore it is important to try to gauge if and how they might need to adapt to possible future architectures. It is equally important to present the requirements of the co-design applications on future machine architectures, so that these might be taken into account in future designs. The impact on some of the CRESTA applications is described in Section 7. Finally, in Section 8 we draw some conclusions on how we believe HPC system architectures are developing towards the Exascale.

# 2.1 Glossary of Acronyms

| ΑΡΙ    | APPLICATION PROGRAMMING INTERFACE                    |

|--------|------------------------------------------------------|

| CAPI   | COHERENCE ATTACH PROCESSOR INTERFACE                 |

| CMOS   | COMPLEMENTARY METAL OXIDE SEMICONDUCTOR              |

| CPU    | CENTRAL PROCESSING UNIT                              |

| CUDA   | COMPUTE UNIFIED DEVICE ARCHITECTURE                  |

| DAG    | DIRECT ACYCLIC GRAPH                                 |

| DSP    | DIGITAL SIGNAL PROCESSOR                             |

| ECC    | ERROR CORRECTING CODE (MEMORY)                       |

| ECMWF  | EUROPEAN CENTRE FOR MEDIUM RANGE WEATHER FORECASTING |

| EUV    | EXTREME ULTRAVIOLET                                  |

| FET    | FIELD EFFECT TRANSISTOR                              |

| FPGA   | FIELD-PROGRAMMABLE GATE ARRAY                        |

| GPU    | GRAPHICS PROCESSING UNIT                             |

| GPGPU  | GENERAL PURPOSE GRAPHICS PROCESSING UNIT             |

| НРС    | HIGH PERFORMANCE COMPUTING                           |

| HSA    | HETEROGENEOUS SYSTEMS ARCHITECTURE                   |

| HUMA   | HETEROGENEOUS UNIFORM MEMORY ACCESS                  |

| IDC    | INTERNATIONAL DATA CORPORATION                       |

| IEEE   | INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS    |

| IFS    | INTEGRATED FORECASTING SYSTEM                        |

| I/O    | INPUT/OUTPUT                                         |

| MPI    | MESSAGE PASSING INTERFACE                            |

| OPENCL | OPEN COMPUTING LANGUAGE                              |

| OPENGL | OPEN GRAPHICS LIBRARY                                |

| OPENMP | OPEN MULTI-PROCESSING                                |

| R&D    | RESEARCH AND DEVELOPMENT                             |

| RDMA   | REMOTE DIRECT MEMORY ACCESS                          |

| SIMD   | SINGLE INSTRUCTION MULTIPLE DATA                     |

| SOC    | SYSTEM ON A CHIP                                     |

| ТВВ    | THREADING BUILDING BLOCKS                            |

| TSMC   | TAIWAN SEMICONDUCTOR MANUFACTURING COMPANY           |

# 3 THE HIGH PERFORMANCE COMPUTING MARKETS

The term "High Performance Computing", or HPC, is becoming more widely known throughout the technology industry and beyond. More companies recognise the value of HPC to their business, particularly as part of the product design process. More scientists are becoming familiar with HPC, whether that is for simulating scientific processes or for data analysis. In short, HPC is starting to be seen as vital for industrial and scientific competitiveness. The consequence of this trend is that the HPC market, as referred to by system manufacturers and market analysts, is becoming deeper, covering a range of systems from the traditional national level supercomputers through to departmental level servers.

| Туре           | Units Sold<br>(2011) | Units Sold<br>(2012) | Growth<br>(%) | Revenue<br>(2011)<br>(Million<br>USD) | Revenue<br>(2012)<br>(Million<br>USD) | Growth<br>(%) |

|----------------|----------------------|----------------------|---------------|---------------------------------------|---------------------------------------|---------------|

| Supercomputers | 2,908                | 2,397                | -17.6         | 4,370                                 | 5,650                                 | 29.3          |

| Departmental   | 3,724                | 3,650                | -2.0          | 1,237                                 | 1,210                                 | -2.2          |

| Divisional     | 20,625               | 17,108               | -17.1         | 3,467                                 | 2,997                                 | -13.6         |

| Workgroup      | 84,294               | 80,692               | -4.3          | 1,226                                 | 1,241                                 | 1.2           |

| TOTAL HPC      | 111,551              | 103,847              | -6.9          | 10,300                                | 11,098                                | 7.7           |

Table 1: HPC Sales by units and revenue. Figures from IDC in [2].

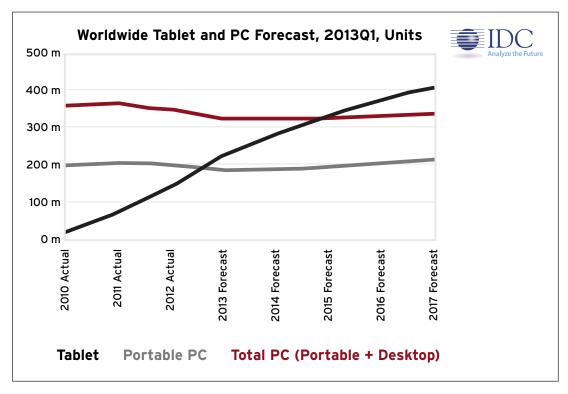

Figure 1: Worldwide Tablet and PC Forecast. Taken from [3].

When looking at the wider technology marketplace it is clear that mobile technology is on a large uptrend; sales of tablets are growing at a rate which will see them overtake personal computers in a few years' time, as shown in Figure 1. IDC expects tablet sales of 229.3 million in 2013 [3]. Meanwhile smartphones are a huge market as well, with that market growing further as they are taken up in emerging economies. When compared to the size of the HPC market in terms of numbers of devices it is clear that the mobile technology market is huge, driving research into low-powered technology. This transformation to a mobile world is driving research forward as consumers are demanding ever more powerful technology with richer, more interactive interfaces, on lighter, more compact devices. Will the drive for Exascale machines, with the widely publicised power budget of 20 MW, be able to capitalise on this mobile technology?

On the other hand, it is also clear from Table 1 that the large, supercomputer segment of the market is providing strong revenue growth. IDC estimates that the HPC market overall will continue to grow at a rate of 6.8%, revenues reaching \$15.4 billion by 2017. As HPC take-up becomes more widespread does the scale of these large machines, with millions of processors, mean that the market will be able to sustain either independent or additional research? One answer to this may come from looking at the growth of accelerators in HPC. When GPUs began being programmed by scientific researchers it was using graphics languages such as OpenGL, however Nvidia clearly recognised several years ago that there was enough of a market to justify the development of CUDA to ease programmability, and in fact now sells a range of GPGPUs specifically for technical computing.

It should also be remembered that the largest machines in the world, those at the very top of the TOP500 list [4], are rarely developed by vendors solely to satisfy the gap in the market. They are usually supported by national scientific or defence agencies that wish to gain access to ever larger machines to support their research. This support is then able to be capitalised upon by the vendors who are able to use any new technology developed for these machines in product lines which they can sell in the wider HPC and non-HPC markets. This explains why support is usually provided within national boundaries – governments are willing to fund research if it will provide a boost to their own economies.

Along with national competitiveness it is also worth remembering that the largest systems, especially the system at the top of the TOP500 list, carry with them some amount of national pride. This will certainly be the case for the first Exascale machine, and therefore provides a motivation for some governments to invest in research in the HPC area.

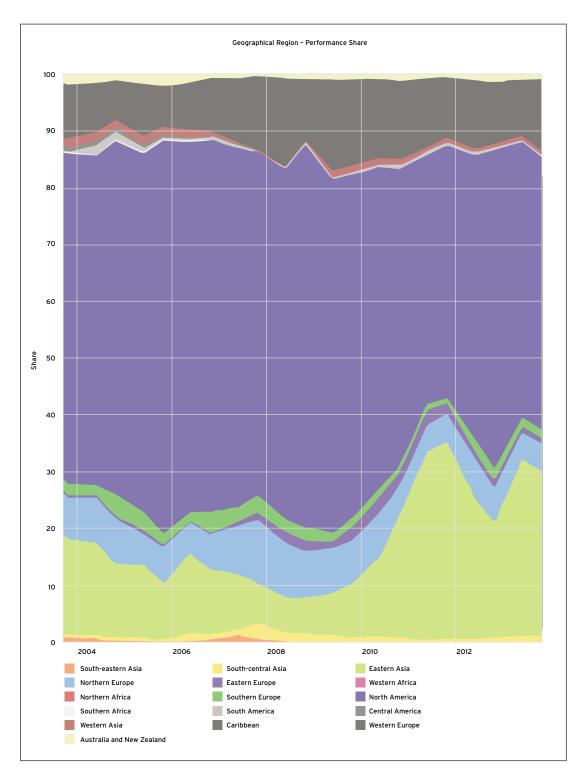

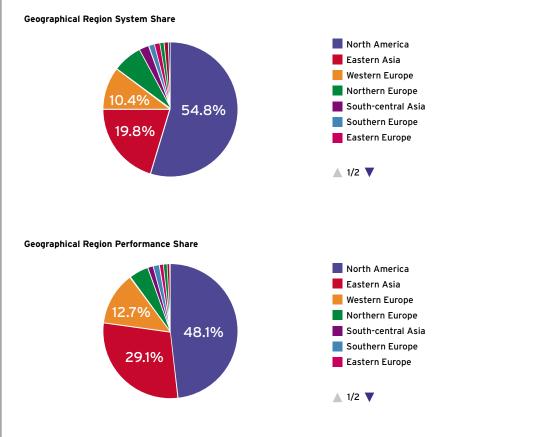

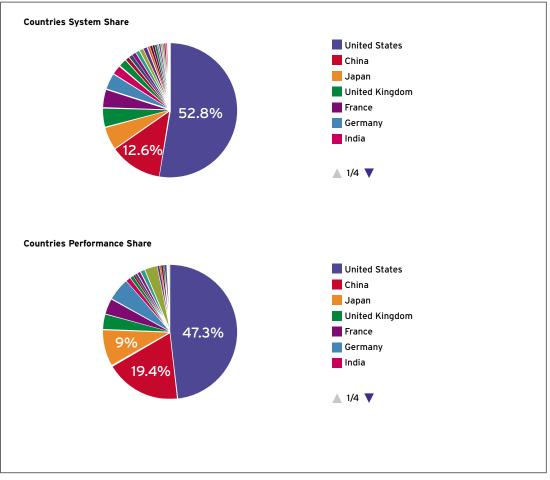

We should therefore look at the international spread of supercomputing today. Such data may be obtained from the TOP500 list. The latest list, from June 2013, may be analysed using the tools available on the TOP500 website to obtain the plots shown in Figure 2, Figure 3 and Figure 4. It is clear from these figures that HPC use is widely spread throughout the world. Although Japan has long been a competitor on the global scene, the recent growth of the market in China has clearly been behind the increase in the share of the market in East Asia. In fact IDC has shown that the Chinese HPC market grew steadily over the last few years, in comparison to others which faltered somewhat during the economic turmoil of the period. This is illustrated by Figure 2, which shows that although North America is still the dominant region, the share of performance in Eastern Asia has grown over recent years. Figure 4 shows that China currently has the second largest share of performance in the TOP500, due largely to the number one machine, Tianhe-2, and the number ten machine, Tianhe-1A. IDC confirms that the Chinese supercomputer segment has grown most heavily of the last few years, and has not been affected at all by the recent recession [2].

Figure 2: Evolution of the geographical share of the performance in the TOP500 list over the last ten years (November 2003 to November 2013).

| Geographical Region       | Count | System<br>Share (%) | Rmax<br>(GFlops) | Rpeak<br>(GFlops) | Cores      |

|---------------------------|-------|---------------------|------------------|-------------------|------------|

| North America             | 274   | 54.8                | 120,339,438      | 172,127,417       | 10,028,289 |

| Eastern Asia              | 99    | 19.8                | 72,809,408       | 121,008,742       | 6,712,672  |

| Western Europe            | 52    | 10.4                | 31,768,483       | 38,317,247        | 2,084,340  |

| Northern Europe           | 36    | 7.2                 | 11,670,158       | 14,513,703        | 844,844    |

| South-central Asia        | 12    | 2.4                 | 3,040,297        | 3,812,719         | 188,252    |

| Southern Europe           | 7     | 1.4                 | 3,864,640        | 4,570,521         | 286,400    |

| Eastern Europe            | 7     | 1.4                 | 2,302,522        | 3,826,340         | 208,284    |

| Australia and New Zealand | 5     | 1                   | 2,180,151        | 2,635,546         | 145, 036   |

| Western Asia              | 5     | 1                   | 1,479,371        | 2,563,830         | 163,696    |

| South America             | 3     | 0.6                 | 626,000          | 1,182,104         | 58,880     |

Figure 3: Geographical share of the November 2013 TOP500 list.

Figure 4: Share of the November 2013 TOP500 list by country.

We can say that progress towards Exascale systems may therefore come from three areas. Firstly, the explosion in mobile technology driving progress in low power technology. This is important given the need for Exascale systems to be provided within a limited power budget. Secondly, the growth in the HPC market, particularly amongst the largest systems. Thirdly, government funded research, whether that is for competitive reasons or for national pride. Progress in technology means it is inevitable that the Exascale will be reached one day, however, external funding sources will necessarily determine the timescale.

# 4 CURRENT TECHNOLOGY TRENDS

In this section we look at current technology trends, both underlying technical trends and market trends - sometimes it is difficult to disentangle the two. We consider basic technologies and system building blocks.

# 4.1 Underlying Basic Technologies

## 4.1.1 Semiconductor Technology

Historically developments in semiconductors have been described in terms of Moore's Law [5], which is commonly formulated as an observation that the number of transistors on an integrated circuit doubles approximately every two years. This has held true for almost fifty years, driven largely by advances in CMOS manufacturing, in particularly photo-lithography techniques which have continually reduced the feature size of integrated circuits. Recently, more advanced processes have been required, such as FinFET or tri-gate transistors, as used by Intel in their "Ivy-Bridge" and "Haswell" processor ranges. These are three-dimensional processes used at scales of 22 nm and below. Future improvements to processes, for example Extreme ultraviolet lithography (EUV), will be required to reduce feature sizes further.

Taiwan Semiconductor Manufacturing Company Limited (TSMC) is one of the major semiconductor manufacturers, counting Nvidia and AMD amongst its clients. Recent presentations of its roadmap [6] have 10 nm manufacturing nodes coming online in 2016. Other innovations presented include 3D chip stacking and the introduction of germanium to replace silicon in order to reduce the feature size even more. Other manufacturers are researching techniques such as carbon nanotubes and other types of semiconductor. Intel has presented their roadmap with aims to go to 5 nm [7].

All indications, therefore, are that Moore's Law will continue to be followed by the chip manufacturers, at least on the timescale of a future Exascale machine around 2020, and probably beyond.

It is more interesting to look at the capabilities of the main semiconductor manufacturers, as shown in Figure 5. This clearly illustrates that a very small number of manufacturers dominate the landscape at small feature-sizes. The main reason for this, as reported in reference [8], is the growing cost of manufacturing as the size decreases and the complexity increases. It becomes harder for companies to design and have manufactured small runs of specialist components as the cost increases. A figure quoted in [9] states that a manufacturer producing 20 nm SoC units with a \$20 average selling price needs to ship over 9 million units to break even. Although this may sound like a large figure it is worth remembering that future Exascale machines will likely contain millions of compute cores, therefore it does not seem infeasible that a manufacturer may produce at least a variant of an existing SoC design targetted explicitly at HPC.

The impact for future Exascale machines is that HPC manufacturers are likely to have to rely largely on commodity components designed for major markets, or else spend more on specialist components. An exception to this may be if FPGAs become more widely used, although so far these have proved hard to program, and therefore their takeup has been limited in HPC.

|                                                                                | 130nm | 90nm | 65nm        | 45/40nm     | 32/28nm | 22/20nm |

|--------------------------------------------------------------------------------|-------|------|-------------|-------------|---------|---------|

| Altis Semiconductor                                                            | •     |      |             |             |         |         |

| Dongbu HiTek                                                                   | •     | •    |             |             |         |         |

| Freescale                                                                      | •     | •    |             |             |         |         |

| Fijitsu                                                                        | •     | •    | •           | •           |         |         |

| GlobalFoundries                                                                | •     | •    | •           | •           | •       | •       |

| Grace Semiconductor                                                            | •     | •    |             |             |         |         |

| IBM                                                                            | •     | •    | •           | •           |         |         |

| Infineon                                                                       | •     | •    | •           |             |         |         |

| Intel                                                                          | •     | •    | •           | •           | •       | •       |

| Renesas (NEC)                                                                  | •     | •    | •           | •           |         |         |

| Samsung                                                                        | •     | •    | •           | •           | •       | •       |

| Seiko Epson                                                                    | •     | •    |             |             |         |         |

| SMIC                                                                           | •     | •    | •           | •           |         |         |

| Sony                                                                           | •     | •    | •           |             |         |         |

| STMicroelectronics                                                             | •     | •    | •           | •           | •       |         |

| Texas Instruments                                                              | •     | •    | •           |             |         |         |

| Toshiba                                                                        | •     | •    | •           | •           |         |         |

| тѕмс                                                                           | •     | •    | •           | •           | •       | •       |

| UMC                                                                            | •     | •    | •           | •           | •       |         |

| Production capabilities ir<br>manufacturers (2011) from<br>Source: IHS iSuppli |       |      | for main se | miconductor |         |         |

Figure 5: CMOS production capabilities. From [8].

## 4.1.2 Communication

Communication is critical to a supercomputer; the high speed, sometimes custom, interconnect is after all the feature which distinguishes a supercomputer from a collection of servers, allowing processors to communicate with each other to co-operate on a computation. However, even on a more basic level communications are critical to any computer. Data needs to be moved between memory and processor, and even within a processor, before it is communicated to the outside world. However, it now costs much more energy to move data in and out of a processor than it does to perform the computation. Therefore reducing this cost becomes critical to the power efficiency of a device, whether that be a mobile device or a supercomputer.

Possible solutions to this problem come in two forms. Firstly, by lowering the distance between processor and data; and secondly, by reducing the cost of the data movement. The first may be achieved by stacking memory directly on top of processors, making a true SoC. This presents a technical challenge to the semiconductor manufacturers, but is under study. The second may be achieved by moving more towards optical communications rather than electrical ones, in the form of silicon photonics. This may be in the form of connecting system boards, or even chips on an individual circuit board.

# 4.2 System Building Blocks

#### 4.2.1 Processors

Current processor trends are determined by both technical constraints and market demands. On the one hand, the end of Dennard scaling and the subsequent slow down in the growth of clock frequencies has led to the development of multi-core processors, such that they are now commonplace. On the other hand, the demand for low power usage in both mobile devices and the server market has driven progress in power efficient processor design. It is perhaps informative to look at recent developments and future plans from some of the main processor manufacturers.

Preliminary Worldwide Ranking of the Top 20 Suppliers of Semiconductors in 2012 (Ranking by Revenue in Millions of U.S. Dollars)

| 2011<br>Rank | 2012<br>Rank | Company<br>Name              | 2011<br>Revenue | 2012<br>Revenue | Percent<br>Change | Percent<br>of Total | Cummulative<br>Percent |

|--------------|--------------|------------------------------|-----------------|-----------------|-------------------|---------------------|------------------------|

| 1            | 1            | Intel                        | 48,721          | 47,543          | -2.4%             | 15.7%               | 15.7%                  |

| 2            | 2            | Samsung Electronics*         | 28,563          | 30,474          | 6.7%              | 10.1%               | 25.7%                  |

| 6            | 3            | Qualcomm                     | 10,198          | 12,976          | 27.2%             | 4.3%                | 30.0%                  |

| з            | 4            | Texas Instruments            | 13,967          | 12,008          | -14.0%            | 4.0%                | 34.0%                  |

| 4            | 5            | Toshiba                      | 12,729          | 10,996          | -13.6%            | 3.6%                | 37.6%                  |

| 5            | 6            | Renesas Electronics Corp     | 10,648          | 9,430           | -11.4%            | 3.1%                | 40.7%                  |

| 8            | 7            | SK Hynix                     | 9,293           | 8,462           | -8.9%             | 2.8%                | 43.5%                  |

| 7            | 8            | STMicroelectronics           | 9,375           | 8,453           | -13.2%            | 2.8%                | 46.3%                  |

| 10           | 9            | Broadcom                     | 7,160           | 7,840           | 9.5%              | 2.6%                | 48.9%                  |

| 9            | 10           | Micron technology            | 7,365           | 6,955           | -5.6%             | 2.3%                | 51.2%                  |

| 13           | 11           | Sony                         | 5,015           | 6,025           | 20.1%             | 2.0%                | 53.2%                  |

| 11           | 12           | Advanced Micro Devices (AMD) | 6,436           | 5,300           | -17.7%            | 1.7%                | 54.9%                  |

| 12           | 13           | Infineon Technologies        | 5,312           | 4,826           | -9.1%             | 1.6%                | 56.5%                  |

| 16           | 14           | NXP                          | 3,831           | 4,096           | 6.9%              | 1.4%                | 57.9%                  |

| 17           | 15           | nVidia                       | 3,608           | 3,923           | 8.7%              | 1.3%                | 59.2%                  |

| 14           | 16           | Freescale Semiconductor      | 4,408           | 3,775           | -14.4%            | 1.2%                | 60.4%                  |

| 21           | 17           | Media Tek                    | 3,309           | 3,472           | 4.9%              | 1.1%                | 61.6%                  |

| 15           | 18           | Elpida Memory                | 3,887           | 3,414           | -12.2%            | 1.1%                | 62.7%                  |

| 22           | 19           | ROHM Semiconductor           | 3,267           | 3,170           | -3.0%             | 1.0%                | 63.7%                  |

| 19           | 20           | Marvell technology Group     | 3,393           | 3,113           | -8.3%             | 1.0%                | 64.8%                  |

|              |              | Top 20 Companies             | 200,845         | 196,251         | -2.3%             | 64.8%               |                        |

|              |              | All Others                   | 109,360         | 106,768         | -2.4%             | 35.2%               |                        |

|              |              | Total Semiconductor          | 310,205         | 303,019         | -2.3%             | 100.0%              |                        |

\* Significant impact on growth due to Samsung Electronics acquisition of Samsung Electro-Mechanic's 50% share of Samsung LED Source: IHS iSuppli Research, December 2012

Figure 6: Market share of semiconductor manufacturers. Taken from [10].

Figure 6 shows the market share of different semiconductor manufacturers. It is clear from this that Intel dominates the market. Many of the other manufacturers are not involved in the HPC market at all, being either in the mobile or embedded space. Also comparison with Figure 5 shows clearly that several semiconductor suppliers do not actually manufacture their own devices, relying on the foundries to do so.

#### 4.2.1.1 Intel

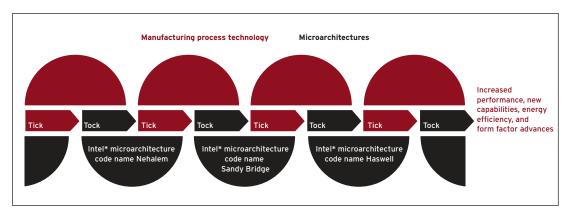

Intel is the largest supplier of semiconductors in the world by market share. It has dominated the processor market for many years with its x86 based microarchitecture. This forms the basis of different product ranges covering mobile, portable, desktop and server markets. Its development now tends to follow the well-known Intel "Tick-Tock" model [11], in which an improvement (a die shrink) in the manufacturing process technology of a "tick" is introduced to a current microarchitecture design, followed some months later by the introduction of a new microarchitecture using this improved process in a "tock". Typically every year there is either a "tick" or a "tock". This is shown in Figure 7, which illustrates the process over recent years. The current microarchitecture is the recently released "Haswell", available on a 22 nm die. This year's "tick" will make this available on a 14 nm process.

Figure 7: The Intel tick-tock model, taken from [11].

The current Intel product ranges include Xeon processors for the server/workstation market, and Core processors for the consumer desktop/laptop market, both based on evolutions of the Core microarchitecture. These are either based on the "Ivy Bridge" microarchitecture which was produced as the result of the shrink of the "Sandy Bridge" architecture to a 22 nm process using FinFET transistors, or the new "Haswell" architecture. Processors within the ranges differ in both their operating frequency, and in the features on offer, such as the number of cores they contain, whether they support Hyperthreading, the amount of cache memory, support for Turbo Boost and their power consumption. For a detailed overview of Haswell see [12].

Some desktop models contain on-die graphics processors in the form of Intel HD or Iris Graphics. Unlike standalone GPUs, use of these graphics cores for technical computing seems to have been limited, however Intel are now promoting their programmability using OpenCL [13], in order to increase their usage in this market. Presently the performance of the integrated graphics also seems to lag that of dedicated GPU cards.

Intel also has the Atom product line of low-power processors aimed at the portable and mobile computing market. Uptake of these seems to be limited compared to ARM processors, however there are recent indications that development of these is being accelerated, with a move to a 22 nm process due later in 2013, but then a rapid move to 14 nm in 2014 [14],[15]. Although initially designed for the mobile market it is also likely that the Atom ranges will see use in low-powered dense servers.

A recent Intel event entitled "Reimagine the Datacenter" [16][18] gave some interesting insights into Intel's future directions. As well as continuing with the low-powered Atom range Intel are also focussed on lowering the power consumption of their Xeon server range. The 14nm shrink of the "Haswell" architecture, known as "Broadwell", will be made available as a System on a Chip (SoC), incorporating I/O and network controllers and accelerators on the same die [19]. The Xeon E3 Haswell is available with a consumption as low as 13 W, therefore it is expected that the Broadwell equivalent will be even lower powered. This can be compared with recent processors, which have a power consumption several times this figure.

Although available only in prototype for some time, a fairly recent product launch from Intel is the Xeon Phi co-processor. This consists of up to 61 x86 cores on a single die, with a high-speed interconnect between them. The cores are derived from an old P5 architecture, but have been augmented with 512-bit vector units amongst other additions. It is able to act as an off-load engine for highly parallel computational tasks in tandem with a traditional Xeon processor, or alternatively to run an executable program itself on a reasonably fully featured version of the Linux operation system. It is utilised in the fastest machine on the TOP500 list, Tianhe-2. In late November 2013 Intel announced "Knight's Landing", the next generation 72-core Xeon Phi, which will be available from 2015. It present a significant revision of the current Xeon Phi processor and promises increased performance per Watt.

#### 4.2.1.2 AMD

AMD are, for all practical purposes, the only competitor to Intel in the traditional x86 processor market. They also produce the Radeon series of GPUs for the desktop and workstation PC market. The market dominance of Intel has often caused AMD to try and differentiate their products in particular markets, rather than compete directly. For instance, the current generation of processors for the server market comprise x86 compatible integer units, which are paired together and share a floating point unit. It has also placed a lot of focus on its accelerated processing units (APUs). These integrate traditional x86 cores with graphics cores. AMD have many years of experience in the GPU area, having acquired the graphics company ATI, and the graphics performance of the AMD processors is currently recognised to be better than that of the Intel equivalent, although still lagging in performance compared with standalone GPUs. Given AMD's expertise in this area the performance gap may well narrow rapidly in the coming years.

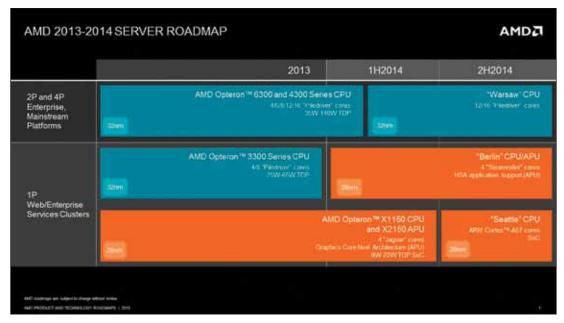

AMD recently presented an update to its server strategy and roadmap [21]. This highlights several interesting developments, with AMD targeting total cost of ownership of servers through low power consumption. The roadmap is shown in Figure 8.

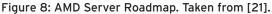

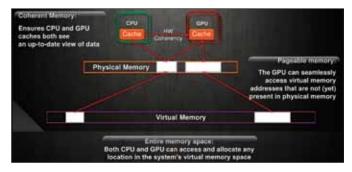

The first chip of interest is the "Berlin" APU. It is the first server processor based on AMD's Heterogeneous System Architecture (HSA), bringing together four standard x86 compatible "Steamroller" cores with a GPU. HSA is interesting to the HPC market as it simplifies programmability of the GPU. AMD is calling the memory architecture heterogeneous Uniform Memory Access (hUMA), as shown in Figure 9 and Figure 10. The CPU and GPU are now able to address the same memory space, removing the need to communicate data between CPU and GPU. Furthermore, HSA provides the same cache-coherency and virtual memory mapping between CPUs and GPUs. As well as easing programmability this also allows for better GPU program management and isolation - up to now there has been no memory protection on GPUs allowing different executables to access each other's data. See reference [22] for more details.

|             | <b>N</b> | UMA         |            |

|-------------|----------|-------------|------------|

| CPU         |          | Memory      |            |

|             |          |             |            |

|             |          | NUMA        |            |

| APU         |          | CPU Memory  | GPU Memory |

| AF0         |          |             | GPU        |

|             | 5        | hUMA        |            |

| APU         |          | Memory      |            |

| with<br>HSA |          | сти сти сти | <b>GPU</b> |

Figure 9: The evolution of AMD's memory architecture. Taken from [22].

Figure 10: Memory layout on AMD's HSA processors. Taken from [22].

Also of interest on AMD's roadmap is the "Seattle". This will be a low powered server SoC, replacing the Opteron X-Series. However, instead of using AMD's own compute core it will use 64 bit ARM Cortex-A57 cores, integrating these with networking components [21]. See reference [23] for a more detailed discussion of this roadmap.

## 4.2.1.3 IBM

IBM's processors are based around the Power Architecture. Firstly it has the Power range of processors, which have been around since the early 1990s. They have been used in IBM's range of servers, generally in large shared memory machines. These have been linked together to form HPC machines using a variety of different interconnects over the years. The current processor is the Power7+, although the Power8 processor was recently announced by IBM at the Hot Chips conference [24], with a release date in 2014. This will be a based on a 22 nm process, and each core is capable of running eight simultaneous threads. Each chip will have an integrated PCI-Express 3.0 controller. IBM has also designed a new transport layer called the Coherence Attach Processor Interface (CAPI) to operate over the PCI-Express 3.0 bus. This layer will allow accelerators such as GPUs or FPGAs plugged into the bus to access main memory. This is a very interesting development for the HPC market.

The other IBM processor used in HPC is of course the PowerPC A2 as used in the Blue Gene/Q. It has 18 cores, of which 16 are used for compute. One is used for operating system services whilst one is a spare that is normally shut down.

#### 4.2.1.4 ARM

The UK company ARM is not a processor manufacturer, but rather a processor designer. It licenses its technology to manufacturers to use in their products. Historically it has specialised in processors with low power consumption, and so ARM processors have been used in mobile phones, tablets and handheld devices. Microprocessor companies manufacturing ARM processors include AMD, Nvidia, Qualcomm and Samsung.

The recent interest in developing low-powered servers for data centre use has prompted ARM to develop a range of 64-bit processors [25]. These have been picked up by a range of manufacturers, typically for use in a SoC. Users include HP, Dell and Calxeda, all of whom typically integrate processor, memory controller, I/O and network controllers on the same silicon.

#### 4.2.1.5 Nvidia

Nvidia's main business is developing high performance GPUs, particularly for the computer gaming market in the form of the various GeForce ranges. However it recognised that its products were being used by some for technical computing, and put some effort into developing general purpose GPUs (GPGPUs). Since then it has developed this range, along with the CUDA language to ease their programmability. They began to be taken up more widely when the GPGPUs were produced with ECC memory and double-precision IEEE compliant arithmetic. The Kepler K2OX model is capable of 1.31 Tflops double precision performance utilising 2688 CUDA cores [26]. The latest model, called K4O, provides even greater performance with 2880 CUDA cores and 1.43 Tflops at double precision.

Nvidia also produce the Tegra SoC for mobile devices [27]. This integrates an ARM CPU, Nvidia GPU, memory controller and I/O in one package. It is currently targeted at mobile devices; however it raises the prospect of future devices being used in HPC.

#### 4.2.1.6 Processor Licensing

The practice of licensing microprocessor designs to other manufacturers has been commonplace for some time. ARM has operated using this model very successfully for quite some time, mainly in the mobile and embedded market. However, as described above, interest in their designs has increased in other areas, mainly due to their low power consumption, but also to provide a processor where a company might not have an existing design. The obvious example of this is Nvidia, who are combining ARM cores with their own GPUs on the Tegra device. It is also interesting to note AMD licensing ARM technology for its own low powered servers, as noted above.

The trend towards SoC can only lead to an increase in this operating model. Companies with existing technology in a particular area, for example interconnect, will likely end up licensing this technology to another company to include on their processor. The alternative to this model is to buy a technology outright; however this is often too costly to contemplate, except for the largest companies. Such an example is Intel, who have recently acquired both the Cray interconnect intellectual property and QLogic's Infiniband program.

However, an interesting development in this area is the entrance of IBM, who have recently announced their intention to license their Power technology. They are doing this through the formation of the OpenPOWER consortium, initially with Google, Mellanox, Nvidia and Tyan [29]. Although IBM have collaborated in the past to license the PowerPC processor technology, as used in the Sony Playstation Cell processor, this is the first time that they will have made available their core Power processor technology. Such a prospect is intriguing for HPC - the suitability of ARM processors for HPC workloads is yet to be proven, whereas IBM's Power processors have a long history of being used in HPC servers. Given the initial partners it is easy to imagine a product integrating Power compute cores, Nvidia GPUs and Mellanox interconnect technology for example; an interesting prospect indeed.

## 4.2.2 Memory

When thinking about HPC machines it is easy to overlook memory technologies – it is usually the CPU that gains all the headlines. An overview of current and possible future directions is given in the CRESTA deliverable D2.1.1 "Architectural development towards Exascale" [1], so that will not be repeated here. Instead we discuss possible issues affecting HPC.

Some HPC applications are already limited by memory bandwidth. Unfortunately the increase in DRAM bandwidth has not kept pace with the increase in FLOPS, particularly when going to multi-core processors, when the bandwidth must be shared between cores. Either increased bandwidth has to be provided in the future by using new technologies, or some applications will need to be completely rewritten. Better communications between processors and memory need to be provided to enable an

increased bandwidth, and one would hope that the trend towards SoC will eventually include memory, perhaps in a stacked design, although it is not clear how close this is to fruition.

The growth in accelerators has led to memory locality issues. Programmers now have to worry about moving data between different memory locations depending upon which part of the system needs to operate on it, the main CPU or an accelerator. However, technologies discussed above such as AMD's hUMA and IBM's CAPI seem designed to overcome this problem. Therefore one hopes it is a short-lived trend and future heterogeneous architectures will provide uniform memory access. Indeed companies such as Convey Computer are looking to provide global virtual addressable memory across heterogeneous architectures.

#### 4.2.3 Interconnect

The interconnect in a supercomputer is critical, and has been lagging behind CPU technology in the same way that memory has. In order to achieve Exascale performance from real applications it is important that this is addressed. The trend towards SoC shown by all manufacturers can only be a good thing; there are signs that, particularly for low-powered data centre chips, the fabric controllers are beginning to be integrated with the CPU. As previously mentioned, silicon photonics are important here.

An interesting development looks to be on the cards from Intel. They look ready to announce a new optical connector called MXC [31][32], based on silicon photonics and new fibre technology. This will allow optical signals to go greater than 300 metres at 25 Gb/s, with a headline peak transfer rate of 1.6 Tb/s. To put this in context, the top-end 12x EDR InfiniBand link provides 300 Gb/s of throughput.

In November 2013 it was announced that Cray had acquired intellectual property rights as well as R&D staff from Gnodal, a UK-based company specialising and leading research into high-performance load-balancing switch fabrics [33].

#### 4.2.4 Software

The current trend towards heterogeneous systems, i.e. traditional CPUs linked with accelerators of some kind, is clearly a challenge for application developers. Currently developers have to worry about managing memory on each device, explicitly moving data between main memory and device memory. Although those looking to exploit the latest technology will always learn the techniques required, it provides a significant barrier to non-expert developers such as scientists who are just attempting to write simulations or analyse their data. It is therefore crucial that the move towards heterogeneous computing is supported by appropriate software tools.

The most obvious example of software supporting adoption of new hardware is in the GPU area. When GPUs started to be used by a few determined individuals for technical computing they were programmed using the shader APIs meant for graphics programming. However, once their usefulness was demonstrated, Nvidia produced the CUDA language extensions for C, which eased their programmability and therefore rapidly accelerated the uptake of GPUs in technical computing and HPC. CUDA is now at version 5.5 and in this latest version supports programming of ARM devices [30]. Portland Group (PGI) also added CUDA extensions were also added by the to their compilers, allowing GPUs to be also utilised by Fortran developers. Recently Nvidia purchased PGI [34], which shows that they see long-term value in the HPC market for their products.

However, CUDA is not the solution for everyone. While useful for exploiting the full performance of GPUs, it still requires developers to explicitly consider the architecture and the movement of data between host memory and device memory. Recent developments such as OpenACC [35] and version 4.0 of OpenMP [36] are aimed at making programmability easier, although developers still have to decide themselves what loops or code fragments are suitable to offload to accelerators. Currently OpenMP 4.0 is not yet implemented, and although OpenACC is supported by the CAPS, Cray and PGI compilers, it is only really available for Nvidia GPUs.

To support its hardware Intel has a well-integrated development suite. To support the recently released Haswell range of processors with inbuilt graphics, Intel announced the Intel SDK for

OpenCL Applications 2013, which allows developers to target both the CPU and GPU components of Haswell. Intel also has their Threading Building Blocks (Intel TBB) [38] for task parallelism, and Cilk+ extensions [39] for multicore and vector processing. It will be interesting to see if any of these gain traction in the HPC market, but this would seem to depend on whether Intel processors come to dominate HPC completely in the future.

Another interesting development is the formation of the Heterogeneous System Architecture (HSA) Foundation, a not-for-profit consortium of SoC designers and vendors, software companies and academia, many from the mobile and embedded space. Partners include AMD, ARM, Qualcomm and Samsung amongst many others, although it is interesting to note that neither Intel nor Nvidia are members. The aim is to make it much easier to program heterogeneous parallel devices including CPUs, GPUs, DSPs and other accelerators. A good overview of an HSA presentation is available at [41]. Here it is explained that a key feature of HSA will be to "move the compute rather than the data". This will be achieved through unified memory addressing so that memory can be allocated on one processor and then a pointer passed to another processor for execution on that data. Although currently available as language libraries the goal is to push HSA as low as possible so that it becomes, for example, a part of the Java virtual machine, and it knows which data to send to which processor. Another aim is to ease programmability. An example shown in [41] shows an increase in performance slightly lower to that gained using OpenCL in C, but with much less code complexity. HSA therefore looks to be a development well worth following, but again whether it gains any traction in the HPC world will remain to be seen.

# 5 SYSTEM ARCHITECTURE TRENDS

Making predictions about future system architectures will always be difficult. A large number of (high-level) factors influence the technology trends that will determine HPC system architectures. It is however possible to draw some conclusions on trends: in the following paragraphs, we will discuss the factors that we believe are most influential in dictating trends in HPC system architectures and then align those with an analysis of historical data. Finally, we will try to make predictions for future systems based on our experience of past developments.

# 5.1 Defining Influences

The following factors are key influences on the architectures of HPC systems:

- performance;

- programmability and usability;

- power usage and efficiency;

- cost of procurement;

- cost of ownership.

The main factor that influences HPC system architectures is that of performance. HPC systems are, by definition, designed to deliver high-end computational power. However, performance alone is by no means sufficient; the most powerful HPC system is worthless if it cannot be exploited, making programmability and usability an equally important factor. An example of high performance, but low (mainstream) programmability is that of FPGAs. They are capable of delivering the high performance required by HPC applications, however they are notoriously difficult to program and use. The issue of poor programmability is slowly being addressed by FPGA vendors, who are increasingly trying to develop sophisticated compilers to support widely used programming models (such as OpenCL) on FPGAs. Nvidia's success in bringing GPUs to the HPC market is only partially due to their potential performance benefits. The fact that Nvidia also developed the CUDA programming model, allowing developers to write programs for GPUs relatively easily without resorting to programming shaders directly, was much more instrumental in the success of GPUs for HPC and technical computing.

Cost of procurement is also a non-negligible factor that influences the types of system architectures. Funding for HPC has not increased in proportion to the performance that is expected of modern systems; we now want much more performance per dollar spent than we did even 5 years ago. The result of this is that commodity components, which due to economies of scale are much cheaper than custom components, have increased in popularity significantly. The use of off-the-shelf products allows the cost of procurement of high-end HPC systems to remain at realistic levels. The ultimate effect is that the HPC market depends on technology that is designed and developed for the consumer market.

The cost of ownership on the other hand keeps increasing at a steady level. The main factors for this are the power and cooling requirements of top-end systems. The current number 1 system in the TOP500 list, Tianhe-2, consumes a total of 24 MWatt, a quarter of which is spent on cooling. It is clear that the current trend in power consumption of HPC systems is not sustainable. Future HPC systems will need to be vastly more power efficient, not only to keep the cost of ownership at a manageable level, but also because there is a limit in the amount of power that can be delivered to a HPC installation.

# 5.2 Trends in the TOP500 list

The first version of the TOP500 list [4] was released in June 1993, providing us now with more than 20 years' worth of data on the most powerful HPC systems. The list not only records system performance (in flop/s), but also additional information such as, amongst others, architecture, interconnect, processors and operating systems. By analysing this information, it is possible to see clear changes in the trends in HPC system architectures over time.

## 5.2.1 Processors

The first processors with more than one core per socket emerged in the TOP500 list in 2001. A big change then happened in 2006-2007, when the share of systems that had single-core processors went from >70% in June 2006 to just under 15% in June 2007. From that point onwards, multi-core processors have been ubiquitous in HPC systems and dual-core sockets were quickly replaced by sockets with four, eight or even more cores. Up until 2006 performance gains could made by increasing a processor's clock rate and thus the number of floating point operations per second it could perform. Physical limitations (such as heat dissipation) however meant that this was an avenue that could not be pursued forever. Instead, processor manufacturers opted for an alternative: increasing the number of processing cores per socket and enabling parallelism at the processor level.

## 5.2.2 Accelerators

Not long after multi-core CPUs, accelerator technologies also started emerging in the TOP500. The first systems with GPGPU cards were listed in 2010. The rationale behind introducing accelerators is similar to that for multi-core CPUs, i.e. it is a straightforward method to add more performance to a machine. Another benefit that GPUs bring is the amount of performance they can deliver per Watt; although GPUs used in the HPC environment are not low power per se, their flops-per-Watt ratio make them a relatively energy efficient solution.

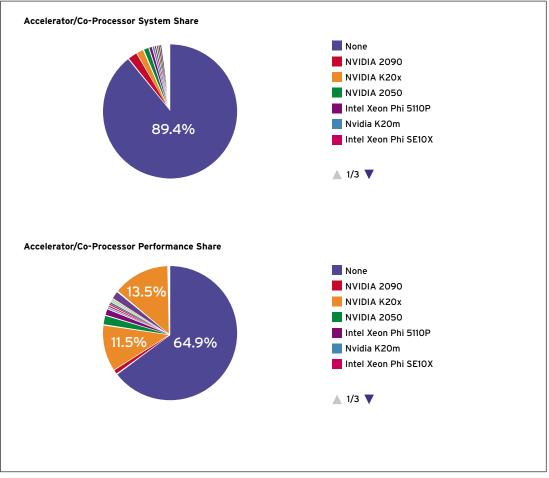

It is clear from the November 2013 TOP500 list that accelerators (both Nvidia GPUs and Intel Xeon Phi co-processors) have made a significant impact in a very short period of time. Although only 11% of systems in the list use accelerators, these systems account for over 35% of the performance of the list – largely because they are present in some of the biggest systems. This is illustrated in Figure 11.

The big question is how long it will be before the main obstacle to good performance with accelerators (i.e. the data transfer between host and device via the PCI Express bus) is a problem of the past? It is already possible to run code completely independently on a Xeon Phi without relying on a host processor, and Nvidia GPU Direct RDMA [42] enables RDMA transfers across an Infiniband network between GPUs, bypassing host memory. Similarly, AMD's hUMA technology enables a shared virtual address space between GPU and CPU.

What is clear from the TOP500 list is the massive parallelism already present in the largest systems, mostly due to the use of accelerators. Core counts of several hundred thousand are seen, and Tianhe-2, at the top of the list, has a total of 3,120,000 cores, comprised of Intel IvyBridge processors and Xeon Phi co-processors. By any stretch of the imagination this number of compute cores presents a massive programming challenge to attempt to utilise them efficiently.

## 5.2.3 System Architectures

In the early days of HPC, supercomputers were largely purpose-built specialist systems constructed from high-end components. They were expensive to design and build and because of this they were not affordable by small organisations such as university departments. Then, during the mid-to-late 1990s, the concept of building small HPC systems from commodity components emerged, suddenly opening the world of (small-scale) supercomputing to a much larger market. This concept of the cluster has evolved over the past 20 years and can now range from small Beowulf-type set-ups all the way to high-end HPC systems (which still rely on mostly commodity hardware) at the top of the TOP500 list. From not being represented at all in the TOP500 list in 1994, clusters represented ~35% of the performance share of all systems in 2003. This has increased to more than 60% in the latest release of the list in November 2013.

Figure 11: Market share of accelerators in November 2013 TOP500 list, taken from [4].

## 5.2.4 Interconnect

The interconnect landscape has changed dramatically over the past 10 to 15 years. In 1999, Infiniband and Gigabit Ethernet came to the market and within a few years these two technologies held more than 50% of the performance share of the TOP500. Recently, the dominance of Infiniband has reduced and custom interconnects (such as can be found in the IBM BG/Q) take an increasingly large performance share. The popularity of solutions such as Gigabit Ethernet and Infiniband can be aligned with the rise (and ethos) of the cluster: they are comparatively cheap interconnect technologies which make HPC accessible to a wide audience.

## 5.2.5 Conclusions from TOP500

The previous paragraphs illustrate one point: a large amount of HPC (though of course not all, the IBM BG/Q being a notable exception) currently relies on commodity off-the-shelf hardware, which is used to build fairly standard clusters that are augmented with accelerators for increased computational power. The evolution of the HPC system over the past 20 years has followed Moore's law, however we have reached the point we are at today partially by moving away from specialist hardware. This has made HPC more affordable and accessible to a wide audience of scientists, and increased competition. However at the same time it has focussed too much on increasing flop/s performance, leaving factors such as memory, interconnect and I/O behind. Only the very top end - the so-called Tier-O systems - are now likely to use purpose-built components.

# 5.3 More Recent Factors

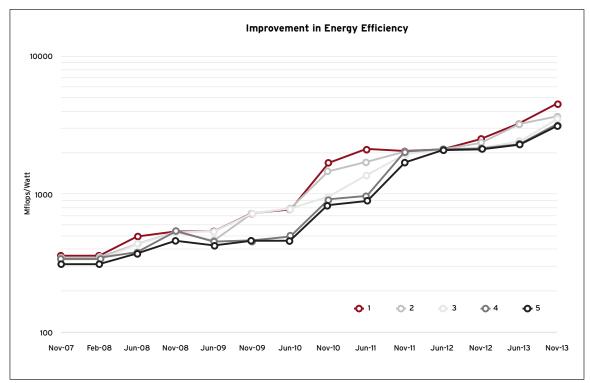

In addition to the TOP500 list, which focuses on the best Linpack performance that HPC systems can deliver, two alternative classification systems have recently emerged: the Green500 list [43] (since November 2007) and the Graph500 [44] list (since November 2010). These lists are analogous to the TOP500 list, but they concentrate on energy-efficiency in the former and data intensive applications in the latter. The Green500 list classifies systems by performance per Watt; it is derived from the results that are submitted for the TOP500. Figure 12 shows how, since the start of the Green500 list less than six years ago, energy efficiency has increased by an order of magnitude. This is testimony to the fact that power usage and energy efficiency are now recognised as real challenges for HPC, especially with a view to the Exascale. However, even using the most energy efficient system today (which can achieve 4503.18 Mflops per Watt), an Exaflop calculation would still require more than 220 MWatts of power.

Figure 12: Evolution of the energy efficiency of the top 5 systems from the Green500 list, since November 2007.

The Graph500 list is interested in the ability of HPC system to perform data intensive tasks and it assesses this ability through graph-related benchmarks and search/optimisation kernels. The metric that is used to rank the system is "billions of edges traversed per second". Since the start of the list in November 2010, this number for the top placed system has gone from 7.08 to 15363. The emergence of the Graph500 list shows that the HPC community is aware of the specialist hardware requirements of this particular HPC application area – the list is an excellent way of tracking evolution and progress.

# 5.4 Future HPC Systems

Having looked at the influencing factors for, and recent evolution of, HPC system architectures in the previous paragraphs, we can draw a few conclusions and make predictions about future architectures:

- Heterogeneous systems are very likely here to stay. They established themselves very quickly on the HPC scene (with GPUs and Xeon Phis) and have brought both improved performance and (where the parallelism can be exploited) power usage. Future systems may become even more heterogeneous and offer several different "cores" per chip; it is not inconceivable that small conventional CPUs may live along side massively parallel chips and possibly even FPGAs, which could be custom-configured to perform specific repetitive calculations (e.g. sparse matrix-vector multiplications). It is clear that programming models would need to support such systems and allow application developers to target the hardware without the need for in-depth knowledge on how to get be best performance out of each different component. Pragma-based models such as OpenACC, or even domain-specific languages with backend code generators could be the long-term solution.

- A lot of commodity components are used in the TOP500 systems, however it is also clear that the very top-of-the-range systems tend to use custom components. This is a reassuring observation, which shows that in order to get the very best performance together with energy efficiency, commodity components that have been derived from consumer products simply will not be a solution long-term. In order to reach the Exascale, HPC vendors must invest in technology that is specific to the market they are targeting. Using gaming, mobile and Cloud technologies as points of inspiration is of course acceptable, but the supercomputing community should not rely on those markets driving the development for HPC.

- Accelerators brought more flop/s, but other factors such as memory, interconnect and system software, have a lot of catching up to do. The emergence of accelerators has maybe allowed vendors to slightly take their eyes off those issues, but they need to be addressed very soon. Future systems will need to have lower-latency interconnects and faster memory.

- None of the lists that were analysed above mention I/O, however this will be one of the great bottlenecks for Exascale systems and one of the areas where a revolution is due.

Future systems will need to have much improved I/O, both through high-performance file systems and an Exascale I/O software stack. HPC applications will of course have to play their part by offloading I/O to separate nodes in a way that is the least intrusive to the computation core of their applications.

- The Green500 has shown a lot of progress in energy efficiency over the past few years, but there still is a very long way to go. The energy efficiency of future HPC systems needs to be increased by an order of magnitude so that the cost of ownership of an Exascale system is realistic and the environmental impact of such as system is kept to as low as possible.

# 6 CASE STUDY: TECHNOLOGY TRENDS AND THE CRAY XC30 SUPERCOMPUTER

The Cray XC30 supercomputer was launched in November 2012 at the annual Supercomputing conference in the USA and represents a major leap in the Cray HPC roadmap. As a completely new engineering product it combines a number of new technologies that were not used in previous generations of Cray supercomputers. The Cray XC30 supercomputer is Cray's first system based on next-generation Intel Xeon E5 processors. Its architecture enables support for a multiple processor line-up of Intel and other x86 processors as well as emerging coprocessors and accelerators. It also introduces the Aries interconnect, using a new system interconnect topology called "Dragonfly". This innovative topology provides scalability in system size and global network bandwidth. Cray continues the evolution of the Cray Linux Environment with the Cray XC30 system, providing a software stack optimized for performance at scale of real-world HPC applications. Cray's programming environment combines flexibility and high productivity features to facilitate effective performance tuning and easy porting. The Cray XC30 system also features increased processor density with high efficiency cooling and power solutions.

The Cray XC30 is the first of Cray's Cascade series systems and the design solution has been influenced by a number of technology, engineering and market trends.

# 6.1 Processor Trends

When the Cray-1 was launched in the mid-1970s, it was based on a custom-designed CPU. Whilst these are principally remembered for the huge vector performance, this was also the fastest scalar processor to date. Almost all applications ran faster on this CPU than on previous systems, even before the rewards of vectorising the codes. Vector processors continued to dominate the HPC market until the mid-1990s, but absolute performance gains were increasingly only seen for well-vectorised applications that took specific advantage of the hardware. Such processors were no longer the fastest for any kind of application. At the same time, the mass market for commodity servers and, to a lesser extent, PCs drove microprocessor speeds higher than those of the more specialist vector processors, and also pushed the price down sufficiently to warrant the design of massively parallel supercomputers. The performance gains across all processor designs also pushed developers to include increasingly complicated physics and chemistry models in their applications. This application complexity made vectorisation increasingly difficult and accelerated the move towards supercomputers based on commodity microprocessors. This trend continues today, with the Cray XC30 being based on the latest Intel Xeon Ivybridge and Sandybridge E5 server processors.

Vector processors have not entirely disappeared; in many ways the current GPUs can be seen as an extension of these and GPUs are increasingly prevalent in HPC systems, including Cray XK7 systems (such as the Titan installation at Oak Ridge National Laboratory) and future Cray Cascade-class systems, which include Nvidia Tesla series GPUs. What has largely disappeared is the commercial viability of developing such custom, HPC-specific vector processors "in-house". Whilst the Nvidia Tesla series GPUs are specialised for HPC computation, their development is driven by the mass-market GPU models sold by the company, which benefit from the same technology. Likewise, development of the Intel Xeon Phi processors (also available in future Cray Cascade-class systems) is tied to the bigger market for Intel CPUs.