# THE EXASCALE DEVELOPMENT ENVIRONMENT State of the art and gap analysis

# **CRESTA** White Paper

Authors: Xavier Aguilar (KTH), Jens Doleschal (TUD), Alan Gray (UEDIN), Alistair Hart (CRAY UK), David Henty (UEDIN), Tobias Hilbrich (TUD), David Lecomber (ASL), Stefano Markidis (KTH), Harvey Richardson (CRAY UK), Michael Schliephake (KTH)

Editors: Mark Parsons, Lorna Smith, Katie Urguhart (UEDIN)

Collaborative Research Into Exascale Systemware, Tools and Applications (CRESTA) ICT-2011.9.13 Exascale computing, software and simulation

# FOREWORD

BY DR STEFANO MARKIDIS, FROM KTH ROYAL INSTITUTE OF TECHNOLOGY, SWEDEN AND DEVELOPMENT ENVIRONMENT WORK PACKAGE LEADER IN CRESTA.

The development and implementation of efficient computer codes for exascale supercomputers will crucially depend on a combined advancement of all development environment components. This white paper presents the state of the art of programming models, compiler technologies, run-time systems, debuggers, correctness checkers, and performance monitoring tools and it identifies the common challenges and problems that need to be solved before the exascale era.

The main focus of this white paper is on emerging and novel technologies in programming models and tools. Together with the traditional approaches, the white paper presents the PGAS parallel programming models and new approaches for programming accelerators, such as OpenACC. It is important that these emerging programming models can be combined with traditional ones for their uptake on exascale supercomputer. For this reason, we discuss in detail the interoperability of different programming approaches. Because we recognize that hand-optimization of parallel codes will be significantly more complex on exascale machines, we present recent progress in software frameworks for automatic tuning and run-time systems to schedule processes on million of computing units. Finally, an overview of the state of the art in parallel debuggers, correctness checkers and performance monitoring and analysis tools is presented focusing on which approaches can provide scalability on exascale machine.

After discussing the state of the art in the field, we analyze the two main common challenges for the developments environment on exascale supercomputers. First, all the components of the programming environments will deal with unprecedented amount of data coming from executing/ debugging/scheduling/monitoring codes running on million computing units, and they will be required to provide responsiveness and interactivity but still introducing minimal overhead. Second, programming tools will need to provide support for novel programming models, such as PGAS, and hardware accelerators, such as GPU and Intel MIC, that will become more and more common on exascale machines.

This white paper provides an overview of different approaches with exascale potential and indicates the progress that are needed to fill the existing gap between petascale and exascale development environment technologies. The results of this white paper guide the current work on development environment in the CRESTA project.

# ABOUT CREST

BY PROFESSOR MARK PARSONS, COORDINATOR OF THE CRESTA PROJECT AND EXECUTIVE DIRECTOR AT EPCC, THE UNIVERSITY OF EDINBURGH, UK.

The Collaborative Research into Exascale, Systemware Tools and Applications (CRESTA) project is focused on the software challenges of exascale computing, making it a unique project. While a number of projects worldwide are studying hardware aspects of the race to perform 10<sup>18</sup> calculations per second, no other project is focusing on the exascale software stack in the way that we are.

By limiting our work to a small set of representative applications we hope to develop key insights into the necessary changes to applications and system software required to compute at this scale.

When studying how to compute at the exascale it is very easy to slip into a comfort zone where incremental improvements to applications eventually develop the necessary performance. In CRESTA, we recognise that incremental improvements are simply not enough and we need to look at disruptive changes to the HPC software stack from the operating system, through tools and libraries to the applications themselves. From the mid-1990s to the end of the last decade, HPC systems have remained remarkably similar (with performance increasing being delivered largely through the increase in microprocessor speeds). Today, at the petascale, we are already in an era of massive parallelism with many systems containing several hundred thousand cores. At the exascale, HPC systems may have tens of millions of cores. We simply don't know how to compute with such a high level of parallelism.

CRESTA is studying these issues and identifying a huge range of challenges. With the first exascale system expected in the early 2020s, we need to prepare now for the software challenges we face which, we believe, greatly outnumber the corresponding hardware challenges. It is a very exciting time to be involved in such a project.

# CREST WHITE PAPERS

BY DR LORNA SMITH. PROJECT MANAGER FOR THE CRESTA PROJECT AND GROUP MANAGER AT EPCC, THE UNIVERSITY OF EDINBURGH, UK.

The CRESTA project has two integrated strands: the first is to prepare a series of key applications for exascale, the second to build and explore appropriate systemware for exascale platforms. Associated with this is a core focus on exascale research: research aimed at guiding the HPC community through the many exascale challenges.

Key outcomes from this research are CRESTA's series of white papers. Covering important exascale topics including new models, algorithms, techniques, applications and software components for exascale, the papers will describe the challenges, current state of the art and propose solutions and strategies for each of these topics.

This white paper is the first in the series, and covers the important challenges associated with the exascale development environment.

# CONTENTS

| 1 | EXECUTI            | VE SUMMARY                                                                  | 1               |  |

|---|--------------------|-----------------------------------------------------------------------------|-----------------|--|

| 2 | INTRODUCTION       |                                                                             |                 |  |

|   |                    |                                                                             | 3               |  |

|   | 2.2                | GLOSSARY OF ACRONYMS                                                        | 3               |  |

| 3 |                    | MMING MODELS                                                                | 4               |  |

|   | 3.1 TRADI<br>3.1.1 | TIONAL PROGRAMMING METHODS                                                  | 4               |  |

|   |                    | Basic Languages<br>Parallelisation Methods                                  | 7               |  |

|   | 3.2 CURR           | ENT PROGRAMMING MODEL USAGE                                                 | 9               |  |

|   | 3.2.1              | PRACE Survey                                                                | 9               |  |

|   | 3.2.2              | CRESTA Co-Design Applications                                               | 10              |  |

|   | 3.3 SUITA          | ABILITY FOR FUTURE ARCHITECTURES                                            | 11              |  |

|   | 3.3.1              | Increasing Numbers of Cores                                                 | 11              |  |

|   |                    | Vector Hardware                                                             | 12              |  |

|   |                    | Accelerated Hardware                                                        | 12              |  |

|   |                    | Node Level Computational Performance                                        | 12              |  |

|   |                    | L PROGRAMMING METHODS                                                       | 13              |  |

|   |                    | Partitioned Global Address Space (PGAS) Languages<br>GPU Programming Models | 13<br>15        |  |

| 4 |                    |                                                                             |                 |  |

| 4 |                    | ILERS FOR EXASCALE COMPUTING                                                | <b>19</b><br>19 |  |

|   | 4.2 AUTC           | TUNING                                                                      | 21              |  |

|   |                    | Novel Autotuning Tools                                                      | 22              |  |

|   | 4.2.2              | Autotuning in CRESTA                                                        | 22              |  |

|   |                    | IME SYSTEMS                                                                 | 23              |  |

|   |                    | Novel Runtime Systems                                                       | 23              |  |

|   |                    | Suitability for Future Architectures                                        | 26<br>27        |  |

| _ |                    | Energy-Aware Approaches                                                     |                 |  |

| 5 |                    |                                                                             | 28              |  |

|   | 5.1 PERFC          | DRMANCE MONITORING<br>Workload Monitoring                                   | 28<br>28        |  |

|   | 5.1.2              | Application Monitoring                                                      | 29              |  |

|   | 5.2 SUIT/          | ABILITY FOR FUTURE ARCHITECTURES                                            | 31              |  |

|   | 5.2 5017           |                                                                             | 31              |  |

|   | 5.2.2              | Resilience and Fault-tolerance                                              | 32              |  |

|   | 5.3 RECE           | NT PERFORMANCE ANALYSIS TOOLS AND FUTURE RESEARCH                           | 33              |  |

### 6 DEBUGGERS AND CORRECTNESS CHECKING TOOL

| 6.1 | TRADITIONAL | DEBUGGERS | AND | CORRECTNESS  |

|-----|-------------|-----------|-----|--------------|

| 0.1 | INADITIONAL | DEDGGGERG |     | CONNECTIVESS |

- 6.1.1 Parallel Debugging Tools

- 6.1.2 Correctness Checking Tools

- 6.1.3 Hardware Platform Support

## 6.2 CURRENT DEBUGGER AND CORRECTNESS CHEC

- 6.2.1 Perception of Debugging

- 6.2.2 Existing Bug Scenarios

- 6.2.3 Desired Software Directions

- 6.3 SUITABILITY FOR FUTURE ARCHITECTURES

- 6.3.1 Scalability on Exascale Computing Platform

- 6.3.2 Usability on Exascale Computing Platforms

- 6.3.3 Support for New Programming Models

- 7 GAP ANALYSIS AND CONCLUSIONS

- 7.1 PROGRAMMING MODELS

- 7.2 COMPILATION, AUTOTUNING AND RUNTIME SYST

- 7.3 PERFORMANCE ANALYSIS TOOLS

- 7.4 DEBUGGERS AND CORRECTNESS CHECKING TOO

- 8 REFERENCES

# INDEX OF FIGURES

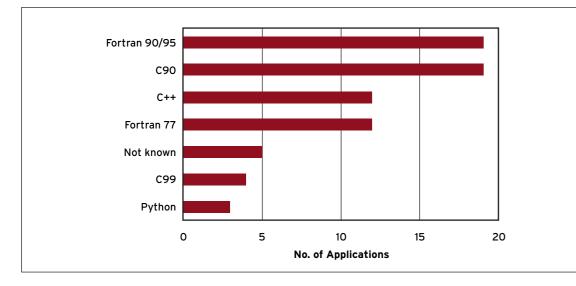

| Figure 1: | Application base languages. Reproduced from [7]                                                    |

|-----------|----------------------------------------------------------------------------------------------------|

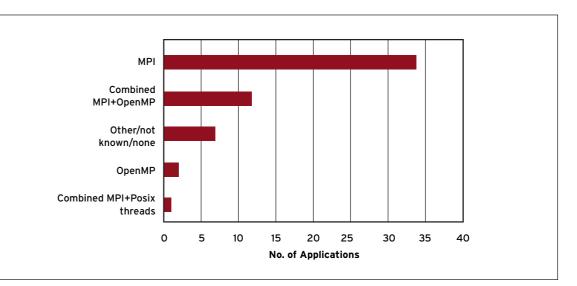

| Figure 2: | Application parallelisation methods. Reproduced f                                                  |

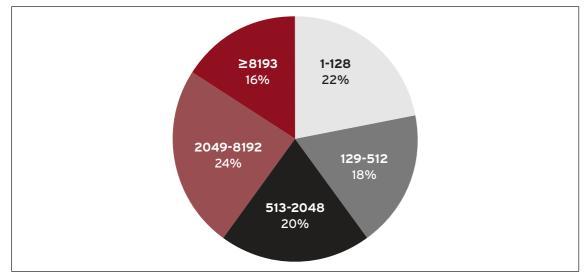

| Figure 3: | Distribution of total utilisation, in terms of number<br>used per application. Reproduced from [7] |

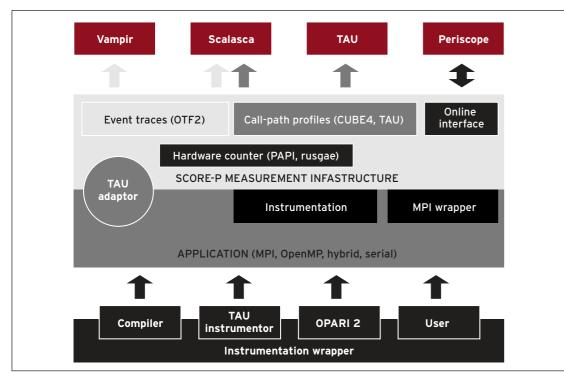

| Figure 4: | Overview of the performance measurement system                                                     |

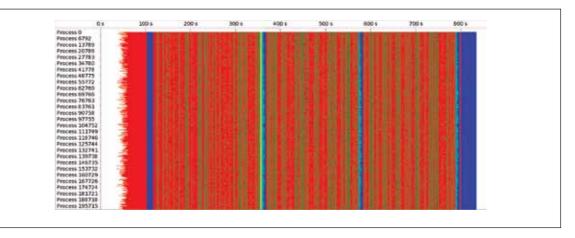

| Figure 5: | Color-coded visualisation of 200,244 processes ov                                                  |

of 850s of the application S3D [68] with Vampir

| LS                         | 35 |

|----------------------------|----|

| CHECKING TOOLS             | 35 |

|                            | 35 |

|                            | 35 |

|                            | 35 |

| CKING TOOL USAGE IN CRESTA | 36 |

|                            | 36 |

|                            | 37 |

|                            | 37 |

|                            | 37 |

| ns                         | 37 |

| S                          | 38 |

|                            | 38 |

|                            | 39 |

|                            | 39 |

| TEMS                       | 40 |

|                            | 41 |

| OLS                        | 42 |

|                            | 45 |

| ]            | 9  |  |

|--------------|----|--|

| from [7]     | 10 |  |

| er of cores  | 11 |  |

|              |    |  |

| em Score-P   | 33 |  |

| over runtime | 34 |  |

| [63]         |    |  |

# **1 EXECUTIVE SUMMARY**

Development environments provide the tools to ease the implementation of scientific algorithms in computer codes, enable applications to run efficiently on parallel supercomputers, allow fast and non-invasive performance monitoring and analysis, and permit prompt detection of code errors. This white paper presents the state of the art for scientific programming development environments, discusses requirements for exascale computing, and outlines the CRESTA project's future strategy to prepare this environment for exascale.

Traditional programming languages (Fortran, C, C++) and parallelisation methods are reviewed. A PRACE survey among 55 applications shows that majority of applications running on European supercomputers are written in Fortran, C and C++. Fortran (Fortran 90/95, Fortran 77) is the most popular. MPI is the most common method to achieve parallelism, while a few applications use a hybrid solution with MPI and OpenMP. Emerging programming models, such as the PGAS languages/libraries (UPC, Co-array Fortran, Chapel, OpenSHMEM), are introduced also. It is very likely that application developers will prefer an incremental approach to a full rewrite in a new language. The programming of GPUs with CUDA, OpenCL, and compiler directives, such as OpenACC, is described. Accelerator directives provide a mechanism for bridging the gap between applications written for the CPU and those ported explicitly to the GPU. The main challenge still remains to deliver an acceptable level of performance using this high-level approach. The current OpenACC directives are unlikely to provide the full functionality to exploit a heterogeneous node. An important task is therefore to ensure that the nascent standards, e.g. as part of OpenMP, evolve in the most productive way for HPC users of heterogeneous architectures.

The state of the art of compilers, automatic tuning tools, and runtime systems is presented. New compiler optimisation technique, targeting exascale computers, are discussed, and different autotuning frameworks, such as Active Harmony and CHiLL, and runtime systems, such as StarPU, StarSS, ForestGOMP, Charm++, and HPX, are discussed. It is shown in this white paper that there has been very promising work in the area of compilers, autotuning and runtime systems. The challenge is to extend these techniques to large-scale distributed memory applications such as those in the CRESTA benchmark suite. With current automatic tuning tools and runtime systems, there is no single approach that meets this challenge. We propose to define a consistent approach that can target mark-up of choices at all the development stages (algorithm choice, source, compilation and launch). This will be done by developing a domain-specific language (DSL) that enables the expression of knowledge, hints and decisions for an efficient execution of an application on exascale supercomputers. Its development will be informed by both the CRESTA co-design applications and open source autotuning projects. If the DSL we develop is general enough then it can be used to wrap specific autotuners without excessive effort. Other runtime services are directed towards the support of dynamic load balancing of application runs on exascale systems as well as using hybrid parallelisation techniques for dynamic adaption of the program to heterogeneous systems.

Existing techniques to monitor and analyse application performance on current petascale computer systems are presented. The Vampir and Score-P performance monitoring and analysis tools have been proven to scale on current petascale supercomputers. However, to raise performance monitoring and analysis tools from petaflop to exaflop scale requires us to develop new methods for monitoring and analysis of information or to combine existing methods to gain a better insight into the system and application by the lowest possible intrusion. To reach exascale performance, the goal is to develop scalable strategies to selectively monitor systems and applications and to use analysis techniques to identify outliers and provide sufficient insights into application and system behaviour. Data mining and reduction techniques will be necessary in exascale computing in order to perform on-the-fly information reduction that will be a requirement for a scalable, automated online performance analysis.

The current state of parallel debuggers and correctness checking tools is presented. The Allinea DDT debugger proved to be scalable on the current petascale computing systems. A survey among CRESTA application experts was completed to understand the current usage of debuggers and error checking tools. This includes information on common implementation errors that application developers make and desirable new features in debugger environments. The survey points out that scalability of debuggers on exascale supercomputers is an important priority for application developers. However, methods to present program state of an exascale application such that developers can understand and pinpoint bugs will also be crucial. Additional main points are the debugger support for new programming models, such as PGAS languages, and the integration of debuggers and correctness checking tools in a unique framework. TU Dresden will work with Allinea to enable the MUST MPI checker to work within the Allinea DDT debugger platform, while also extending MUST's scalability in order to cope with more than just smaller scale test cases.

# 2 INTRODUCTION

As we look forward to the exascale era it is clear that we must face new challenges, not least for the software stack required to support exascale applications. Each component of the development environment (programming models, compilers, runtime systems, performance monitoring and analysis tools and debuggers) needs to fully and efficiently exploit future exascale computing platforms, characterised by two main features:

- Extreme parallelism of the order of hundreds of millions of compute units;

- Heterogeneous computer architecture, where the compute units are a mix of CPUs and accelerators.

Programming languages, parallelisation methods, compilers, autotuning software, performance monitoring and analysis tools, and debuggers should fully exploit concurrency available in future exascale supercomputers. All these tools are expected to run efficiently, and scale reasonably while increasing the number of compute units. In addition, the development tools should support heterogeneous architectures.

The challenges of developing software for future exascale computers have been analysed previously by the IESP, ESSI and PRACE initiatives. This white paper starts from the results presented in their roadmap, white papers and reports, and specifically focuses on the development environment for the CRESTA co-vehicle applications.

This white paper is organised as follows. Section 3 examines the traditional programming models and parallelisation methods, presenting their current usage in the PRACE network and CRESTA co-design vehicle applications. The different levels of hardware parallelism in the current and future computer architecture are then examined. Novel programming models and the programming of GPGPUs with CUDA, OpenCL and compiler directives are discussed. Section 4 presents the challenges of developing compilers to produce an optimised executable code for exascale supercomputers, addresses automatic tuning tools, and discusses the state of the art of current runtime systems. Section 5 presents the performance monitoring and analysis tools available and the new developments in the field. Section 6 presents the state of the art of debuggers and correctness checking tools, their support for programming models and hardware. The usage of debuggers and correctness checking tools in the CRESTA project is analysed. Section 7 concludes the white paper, analysing the gaps to be filled towards the implementation of development environments for exascale computing and summarising the main results.

#### 2.1 Purpose

#### The purposes of this white paper is as follows:

- Present the current status and emerging trends in programming models and parallelisation methods. Emphasis is given to how programming models need to adapt to massive parallelism on different hardware levels and on heterogeneous platforms.

- Present the state of the art and new developments in compiler optimisation techniques and automatic tuning tools.

- Present the state of the art of the runtime systems.

- Present the state of the art in performance monitoring and analysis tools and the challenges of monitoring and analysing the performance of applications running on exascale computer platforms.

- Discuss the current debugger and correctness checking tool performance on petascale computing platform and indicate the new directions in developing scalable debuggers on exascale supercomputers.

- Present the development environment current limitations and gaps that may affect successful implementation for exascale computing platforms.

- Provide directions and guidance CRESTA's strategy for the exascale development environment.

#### 2.2 Glossary of Acronyms

| AGAS | Active Global Address Space           | GPU    | Graphics Processing Unit                     |

|------|---------------------------------------|--------|----------------------------------------------|

| API  | Application Programming Interface     | GPGPU  | General Purpose Graphics Processing Unit     |

| ARB  | Architecture Review Board             | HPC    | High Performance Computing                   |

| BLAS | Basic Linear Algebra Subprograms      | IESP   | International Exascale Software Project      |

| CAF  | Co-Array Fortran                      | MPI    | Message Passage Interface                    |

| CUDA | Compute Unified Device Architecture   | NUMA   | Non-Uniform Memory Access                    |

| DRAM | Dynamic Random-Access Memory          | 00     | Object Oriented                              |

| DSL  | Domain Specific-Language              | OpenCL | Open Computing Language                      |

| DSM  | Distributed Shared Memory             | OpenMP | Open Multi-Processing                        |

| DSP  | Digital Signal Processor              | ORNL   | Oak Ridge National Laboratory                |

| EC   | European Commission                   | PGAS   | Partitioned Global Address Space             |

| EESI | European Exascale Software Initiative | PRACE  | PaRtnership for Advanced Computing in Europe |

| FFT  | Fast Fourier Transform                | RDMA   | Remote Direct Memory Access                  |

| FIFO | First In, First Out                   | SM     | Stream Multiprocessors                       |

| FLOP | FLoating point OPerations             | SPMD   | Single Program Multiple Data                 |

| FPGA | Field-Programmable Gate Array         | UPC    | Unified Parallel C                           |

# **PROGRAMMING MODELS** 3

#### **Traditional Programming Methods** 3.1

#### 3.1.1 Basic Languages

Many hundreds of programming languages and (to a lesser extent) communications models have been developed during the last decades, but it is fair to say that High Performance Computing is dominated by an extremely small subset of well-established programming models (as we demonstrate in Section 3.2). In terms of languages, almost all applications seen on typical HPC systems today are written in Fortran, C or C++, sometimes mixing these. Here we review these languages.

#### 3.1.1.1 Fortran

With its development starting in 1953, Fortran was one of the first high-level programming languages and has been in constant use for nearly sixty years.

The language was developed with a view to efficiency and hence the structure of programs is relatively constrained, making it easier for the compiler to produce efficient code. In established compiler suites, there is a long history of performance optimisation for Fortran, which adds to the performance advantages.

There was an early decision (dating back to FORTRAN66) to standardise the language using internationally recognised standards bodies, ANSI (for FORTRANs 66 and 77 and for Fortran 90) and ISO/IEC (for Fortrans 95, 2003 and 2008). This made the language attractive to HPC users looking for portability of applications between compiler and hardware vendors.

Early support for double precision and complex intrinsic numeric data types (added in FORTRAN II in 1958) also cemented the language's appeal for scientific computing. Good support for multidimensional arrays and enhancements like modules enhanced the appeal of Fortran for many scientific applications. The maintenance of backward compatibility between Fortran versions has also facilitated application longevity.

A number of compilers now advertise full compliance with the Fortran 2003 standard. Although none yet have full support for the Fortran 2008 standard, the Cray Compilation Environment (version 8.0, released December 2011), for instance, has partial support including for submodules and co-arrays [1]. The main strength of Fortran is that the language is deliberately restrictive to the programmer, which gives the compiler better scope to either produce highly optimised code or to carry out strict runtime checks of code correctness (e.g. bounds checking).

The main disadvantages of Fortran are that the language is traditionally poor at interacting with the Operating System, does not handle string manipulations well and that it is difficult to manipulate unformatted data files. These problems have been at least partially addressed in Fortran 2003, but the usual solution has been to mix in some C routines. Despite the language changes in Fortran90 onwards, Fortran is often viewed as an old-fashioned programming language and most universities no longer teach it as standard.

### 3.1.1.2 C

The C programming language was originally developed between 1969 and 1973 to help realise the Unix operating system.

The language was not formally standardised until 1989 (by ANSI, then adopted by ISO in 1990 and known interchangeably as C89 or C90), but prior to this the book by Kernighan and Ritchie [2] widely acted as a de facto definition of the language. Since then, a C99 standard has been released. As with Fortran, backward compatibility was largely maintained during these revisions.

Δ

Historically, performance of C applications was hampered by the extensive use of pointers to reference data arrays. This makes it difficult for the compiler to guarantee independence of data operations, which is needed when optimising (and also when parallelising) compiled code. Many compiler vendors have introduced ways to indicate independence (e.g. through pragmas), but this is not guaranteed to be portable. C99 has improved this somewhat, e.g. by introducing the restrict qualifier to indicate independence.

C has two particular strengths in HPC. On systems running a Unix or Linux-based operating system, the programmer has good access to the underlying OS, including environment variables and command line arguments. This is particularly useful when profiling a code and understanding the relationship between application performance and the system state (memory usage etc.). The other strength is the ability to handle raw data files produced, for instance, by third party applications on different computing architectures.

C also has good string handling properties. Sociologically, it is often viewed as being a more modern programming language than Fortran, although, given its age, this is perhaps more because C++ and Java are based on C, rather than C itself being modern. Again, C is only taught in a minority of universities now.

In C, the user has far more control over memory management and this can make it harder for the compiler to produce highly optimised code or to verify code correctness. With modern compilers, however, a lot of these problems have been overcome and for many scientific codes the performance difference between Fortran and C is negligible. In addition, modern Fortran versions also now have improved interfacing abilities with the OS.

### 3.1.1.3 C++

C++ was developed between 1979 and 1983 by Bjarne Stroustrup. Starting as an extension to C, the language was not standardised until 1998 (by ISO), with a technical corrigendum in 2003 and a new standard known as C++11 in 2011. C++ has only recently been used in HPC, largely because the complexity of the language and the shortage of highly optimising compilers. Fortran and C are largely procedural languages, with the program organised as a set of distinct subprograms that are explicitly called in the code. This leads to a calltree-based structure for an application profile.

C++ can be used in this way (being a superset of C), but it also offers great scope for the programmer to use a variety of software engineering methods to produce well-organised, understandable, maintainable and extensible code. These methods include: object oriented (OO) programming methods and data-hiding, where data is packaged into objects that also include methods for accessing and modifying the information; template metaprogramming and const correctness. The classic problem with using C++ in HPC is that the more high-level features are used in the code, the harder it becomes for the compiler to produce optimised code. The encapsulation of methods in objects makes it hard to predict the independence of statements in the code and the packaging of data often leads to poor layouts of data in memory that lead to poor cache utilisation in repeated operations such as loop iterations.

These problems can be reduced by C++ programming techniques such as templating, but the large amount of knowledge needed to start using these is often a barrier to uptake. The advantage of C++ is that, correctly used, it can abstract the user from the underlying architecture and choice of communications model(s). This must be balanced against the careful programming needed to allow efficient code execution and the possible lack of compiler portability that comes from using such advanced programming techniques. C++ is also seen as being a modern language, with many universities teaching it in the view that this provides a useful employment skill for undergraduates.

#### 3.1.1.4 Fortran/C/C++ interoperability

Given the complementary strengths of Fortran and C, there is a long tradition of mixed language compilation. Different parts of the application may be written in either Fortran or C, as appropriate, and separately compiled to object files that are then linked into a single executable.

In Fortran, data objects may be passed to subprograms simply by reference that matches the mechanism used by C when a pointer is passed. Arrays of data can therefore be presented in the two languages as contiguous chunks of memory. Given that Fortran and C array elements have different orderings in memory (in Fortran, the leftmost index has unit stride in memory, whereas in C it is the rightmost), care must be taken to access data in a consistent manner in the two languages.

Prior to the Fortran 2003 standard, however, it was difficult to mix Fortran and C in a completely portable fashion. Clearly the same levels of precision (i.e. number of bytes per data item) must be used, but this cannot be guaranteed. For instance, whilst it is almost universally true that INTEGER in Fortran and int in C both use 4 bytes, this is not specified in any language standard. Neither was there any way to check for any incompatibility when cross-calling between languages, either within the program or through compile-time type checking. There is also no guarantee of runtime errors, although most mismatches rapidly lead to floating point exceptions or similarly trappable errors.

Linking of the two languages was also complicated by compiler-dependent additions of trailing underscores to, or even capitalisation of, subprogram names in object files. Whilst some compilers offer options to control this, some investigation usually involving trial-and-error or running the Unix nm command (often filtered using grep) on the object files was required. This exercise would then be repeated each time the Fortran or C compiler was changed or a new computer architecture was available.

Fortran 2003 represented a milestone in compatibility, providing a standardised mechanism for interoperating with C. This is done through an intrinsic module named iso\_c\_binding that contains information about the type parameter values for intrinsic types. There are also mechanisms for ensuring the compatibility of memory address pointers and of global and passed data. Finally, there is also a consistent way to call Fortran procedures from C and vice versa with Fortran INTERFACEs offering compile-time type-checking for passed arguments.

Whilst this was not formally standardised until Fortran 2003, many Fortran95 compilers have supported this interoperability for a number of years. Nonetheless, many applications use the "traditional" non-portable linking, partly due to inertia and partly because of the perceived (but necessary) complexity of the iso\_c\_binding module.

C++ is a much more complicated language than either C or Fortran, so interoperability can be more difficult. If the object oriented programming techniques are sparingly used, C++ is directly compatible with C and, by extension, with Fortran. If, however, the more advanced features of C++ are exploited, interoperability is harder to arrange. Currently, most applications do not attempt to mix C++ with C or Fortran as part of the user code. Libraries written in either C or Fortran are called from within C++ codes, but this is usually achieved by passing pointers to contiguous memory segments that hold the relevant data. As such, this mandates the user to abandon, at least temporarily, the OO principles of data hiding and encapsulation.

With no type-checking of passed data, care must also be taken that the same levels of precision are used in both Fortran and C. Care must be taken to arrange that passed arrays of data are accessed by the two languages in a consistent manner.

#### 3.1.1.5 Python

Python and, to a much lesser extent, other scripting languages are being increasingly used in HPC applications. In contrast to the previous languages, python is not typically used to directly develop key kernels in HPC applications. More usually, it is used either as a wrapper to control job launch parameters or as a runtime framework to tie together kernels written in compiled languages. The latter is made possible through the integration of, for instance, MPI in python.

The motivation for this is that python has a reputation (largely justified) for providing a way to rapidly and flexibly develop large amounts of code, building on a wide range of existing libraries (known as modules). Given the oft-cited rule of thumb that 80% of the runtime of a typical scientific application is spent in 20% of the code, python is a suitable choice for coding the remaining, non-performancecritical 80% of the application.

Although there is undoubtedly a small performance sacrifice in doing this, the main disadvantage to using python in this way is the current lack of efficient parallel runtime support. As an example, the startup time of the application can become enormous when scaling to large numbers of MPI ranks as each python process separately attempts to load the same module files. These problems are surmountable, but as only a minority of python users (and developers) are using it in an HPC environment, it is not yet clear how this will be achieved.

#### 3.1.2 Parallelisation Methods

Here we introduce the most common methods of achieving parallelism in HPC applications.

#### 3.1.2.1 OpenMP

The OpenMP API [3] is arguably the simplest model for adapting a serial application to allow it to utilise multiple compute cores in parallel, with the key restriction that these cores must operate on the same memory address space: it can be used to parallelise code within multi-core workstations or single nodes of larger system. To be effective for large-scale problems it must be combined with other "distributed-memory" parallelisation techniques.

Before the emergence of the OpenMP standard, there were several hardware vendors offering shared-memory systems but each provided a different compiler with different sets of directives to allow use of multiple threads or vector units, making it hard to write portable code. The OpenMP forum, consisting of major vendors plus academic organisations, released the first OpenMP standard (supporting Fortran only) in October 1997, followed by a revision supporting C/C++ in 1998. Further revisions since then have improved, clarified and expanded the standard.

The model is based on the concept of "threads", which are like processes, except that they can share memory with each other (as well as having private memory). While serial applications only follow a single thread of execution (and hence only utilise a single core), OpenMP allows the use of multiple threads, with the idea that the work in the application can be distributed onto multiple cores. OpenMP provides a set of extensions to Fortran, C and C++, consisting of compiler directives, runtime library routines and environment variables.

The parallel region is the basic parallel construct in OpenMP, which defines the section of the program that is to be executed in parallel. The program begins execution on a single thread (the master thread), and when the first parallel region is encountered, the master thread creates a team of threads. Every thread executes the statements inside the parallel region. At the end of the parallel region, the master thread waits for the other threads to finish, and continues executing the next statements. OpenMP has directives that indicate that work should be divided up between threads. Since loops are the main source of parallelism in many applications, OpenMP has extensive support for parallelising loops. A Fortran example is as follows:

!\$OMP PARALLEL !\$OMP DO do i=1,n b(i) = (a(i)-a(i-1))\*0.5 end do !\$OMP END DO !\$OMP END PARALLEL Without the directives inserted, the loop would just execute on a single core. The combination of the "parallel" and "do" directives instruct the compiler to split the loop into multiple sub-loops, to be executed by multiple threads in parallel. The number of threads to be used can be controlled through an environment variable or runtime routine, and there are a number of options to control which loop iterations are executed by which threads. It is up to the programmer to ensure that the iterations of a parallel loop are independent. Only loops where the iteration count can be computed before the execution of the loop begins can be parallelised in this way.

Recent versions of OpenMP also support the concept of tasks, which provide a mechanism for parallel execution of code regions where loop-based decompositions are not suitable. The concept of "tasks" was added to the OpenMP standard when version 3.0 was released in 2009. OpenMP tasks allow the parallelisation of certain types of algorithms that are not amenable to straightforward use of loop directives (for example the traversal of linked lists or trees, with operations on each element). The task construct defines a section of code to be packaged up for execution. Multiple tasks can then be executed in parallel by the multiple threads in a parallel region. A new "task wait" directive provides a mechanism to instruct the program to wait until all tasks have been completed.

The concept of threads is wider than OpenMP, and it is possible to incorporate threaded programming into sequential programs using lower level APIs such as POSIX threads (pthreads) (on UNIX platforms) but such APIs are typically involve more complex programming, are not fully cross-platform and cross-language (in particular use within Fortran is not straightforward). OpenMP is a portable higher-level abstraction (which, depending on the implementation, may utilise such lower-level APIs internally). The OpenMP approach can be attractive as a way to add incremental parallelism to an application without significant changes.

#### 3.1.2.2 Message Passing Interface

It is usually only practical to use OpenMP to parallelise within a single node of a system. To utilise multiple nodes, each with its distinct memory address space, a distributed-memory parallelisation technique is required. Such methods must include mechanisms for data to be transferred between nodes: i.e. for messages to be passed. The effective message-passing standard is the Message Passing Interface (MPI) [4].

In the 1980s and early 1990s there emerged several message-passing systems with differing syntax but similar goals. MPI was the first effort to produce a message-passing interface standard across the whole parallel processing community. Sixty people representing forty different organisations collectively formed the "MPI Forum" in 1992. A two-year process of proposals, meetings and review resulted in a document specifying a standard Message Passing Interface (MPI).

The message-passing model is based on the notion of processes. One can think of a process as an instance of a running program, together with the program's data. Parallelism is achieved by having many processes co-operate on the same task. Each process has access only to its own data - i.e. all variables are private. Most message passing programs use the Single-Program-Multiple-Data (SPMD) model, where all processes run the same program and each process has a separate copy of the data. To make this useful, each process has a unique identifier and processes can follow different control paths through the program, depending on their identifier (called the "rank").

Processes communicate with each other by sending and receiving messages through library calls from the conventional sequential language such as Fortran, C or C++. In the simplest case one process would call the MPI\_Send routine to send data while another calls MPI\_Recv to receive data. These calls must correspond, leading to the description of MPI as a "double-sided" communication model. The MPI library functions take as arguments, pointers or references to the data structures as well as other information such as the amount of data and the destination/source rank. There are variants to these library calls to give more control and flexibility to tune performance and manage more complex patterns. There also exists a range of functionality for other operations, such as the initialisation/ finalisation of parallel executions, synchronisation, and "collective communications" involving groups of processes (e.g. one process broadcasting data to all others).

MPI is very powerful and flexible: it gives the programmer intricate control to develop a complex parallel program spanning many nodes, and this is why it has become the most popular technique on large-scale supercomputers. This is at the expense of complexity: since it is up to the user to fully manage the distinct memory spaces and task decompositions, MPI programs can become very involved. Also moving an existing application to MPI often requires significant code changes (in comparison to adding OpenMP).

### 3.1.2.3 Hybrid Programming and Interoperability of OpenMP and MPI

Modern systems are comprised of multiple nodes, each with multiple cores and shared resources such as memory. OpenMP programs are usually restricted to a single such node, while MPI programs can span multiple nodes. The simplest way to utilise all cores using MPI is to run with the same number of MPI processes as cores, i.e. treat each core, and associated memory, as a separate "partition" of each node, and not to differentiate between intra- and inter-node communications at the program level (although a well-written MPI library might well do so behind the scenes). Alternatively, one can run with a "hybrid" program containing a combination of MPI and OpenMP. In this case there would be less MPI processes than physical cores, and each MPI process would consist of multiple threads, to ensure utilisation of all cores. A typical configuration is one MPI rank per node or CPU.

Performance can benefit from this approach in a number of ways [5]. By using fewer MPI ranks per node, the memory requirements of the application can be reduced, allowing larger local subproblems in the parallel-decomposed problem and making the performance less reliant on the memory bandwidth. The increased local problem size can increase the efficiency of the local computation. It can also allow further strong scaling of applications that had reached the limits of their parallel decomposition. Using fewer MPI ranks per node also reduces network traffic, which may have particular benefits in collective operations (depending on how the MPI library is written).

The advantages are system and implementation dependent, but are expected to become increasingly important as the number of cores per node increases.

#### Current Programming Model Usage 3.2

#### 3.2.1 PRACE Survey

The Partnership for Advanced Computing in Europe (PRACE) project is tasked with implementing a pan-European High Performance Computing service and the necessary infrastructure [6]. A PRACE deliverable was published in February 2011 that contained the results of surveys designed to gather information on the active HPC systems in Europe, usage profiles and details of the applications using these systems [7].

Figure 1: Application base languages. Reproduced from [7].

Each of the major European HPC service providers was surveyed on applications accounting for greater than 5% of system utilisation. Information was gathered relating to a total of 57 distinct applications. Figure 1 shows base language utilisation (noting that the total number is higher than 57 since some applications use more than one base language). In can be seen that Fortran, C and C++ account for the vast majority of total usage, with Fortran (Fortran 90/95, Fortran 77) being the most popular, followed by C (C90 + C99) and then by C++. The only other reported language is Python, used in a few applications.

#### Figure 2: Application parallelisation methods. Reproduced from [7].

Figure 2 shows the breakdown by parallelisation method. It can be seen that the vast majority of applications used MPI: some of these in combination with OpenMP. Sole OpenMP usage was small (which is not surprising since the systems involved are typically used for relatively large parallel jobs, and OpenMP is suitable for intra-node parallelisation only). The only other reported parallelisation method was that one application used Posix threads (combined with MPI). A comparison with 2008 PRACE survey shows that there has been an increase in the proportion of the applications using C or C++ compared to those using Fortran. The proportion of applications using hybrid MPI and shared memory has increased also compared to the 2008 PRACE survey. The longevity of parallel HPC simulation codes makes it unlikely that there will be major shifts in these patterns over the next five to ten years.

Therefore, the results of this survey indicate that the vast majority of applications use the traditional programming methods and models described in the preceding section.

#### 3.2.2 CRESTA Co-Design Applications

In this section, we briefly summarise the languages and parallelisation methods used in the CRESTA co-design applications. As for the PRACE applications, all use the "traditional" programming models already described.

#### 3.2.2.1 GROMACS

GROMACS is written in C and C++, with optional inline x86 assembly code and/or CUDA. Parallelism is a hybrid of MPI and OpenMP.

#### 3.2.2.2 ELMFIRE

ELMFIRE is mainly written using Fortran90, with some C used for auxiliary functions. The code is single-threaded, with pure MPI parallelism.

## 3.2.2.3 HemeLB

HemeLB is written in C++ with parallelism via MPI. A hybrid version, mixing OpenMP with MPI, is expected in the early part of the CRESTA project.

### 3.2.2.4 IFS

IFS combines Fortran (Fortran90 and Fortran95) with C. The parallelism is implemented using a hybrid of MPI and OpenMP.

### 3.2.2.5 OpenFOAM

OpenFOAM is implemented using C++ with parallelism via MPI only, although some work has been done on hydridising certain solvers using OpenMP.

#### 3.2.2.6 Nek5000

Nek5000 is written using FORTRAN77 and C. Parallelism is via MPI only.

#### Suitability for Future Architectures 3.3

#### 3.3.1 Increasing Numbers of Cores

The PRACE survey discussed in Section 3.2.1 contained another interesting finding.

#### Figure 3: Distribution of total utilisation, in terms of number of cores used per application. Reproduced from [7].

Figure 3 shows a profile of application sizes, in terms of numbers of cores used; 84% of the applications use less than 8192 cores. The peak performance of today's processors is of the order of 10 GFlops/core. Therefore, in order to scale to an exaflop using today's CPUs, applications would have to scale to at least 100 million cores. This highlights the problems we face going forward: even if it were possible to build exascale systems with standard CPU technology, there is an enormous gap in terms of how well applications can scale today and how well they would have to scale to utilise an exaflop.

#### 3.3.2 Vector Hardware

To maximise performance on current and future computing systems, applications must fully exploit each microprocessor in the system, whether it is using a desktop PC or the largest of supercomputers. This means exploiting the parallelism within the chip not just at the "core" level (i.e. running across all cores in parallel) but also, crucially, at the "vector" level (taking advantage of the fact that each "core" can simultaneously process vectors containing multiple data elements). The latest CPUs from Intel and AMD can typically process (double precision data type) vectors of length 4 concurrently. This will increase with future products; the upcoming Intel MIC architecture will debut with vector length of 8. Current Graphics Processing Units (see following section) already process larger vectors (albeit described with different terminology): the latest NVIDIA GPUs operate on "warps" of size 32. Therefore, it is increasingly important that applications are able to actually exploit such vector-level parallelism. Traditional languages such as C and Fortran do not have any mechanisms for exposing this vector-level parallelism; instead there is reliance on compiler auto-vectorisation. However, without extra information and assurances from the programmer compilers often find this a difficult task unless code is written in a very specific way.

#### 3.3.3 Accelerated Hardware

Some early HPC architectures treated special-purpose hardware as an attached resource (for example the AMT DAP) that could be used for parts of an application that could be mapped to the specialist hardware. Increasing miniaturisation has resulted in a family of small integrated products (FPGAs, DSPs and GPUs) that can be integrated on the processor board or attached via a PCI expansion card. One of the most promising is the Graphics Processing Unit (GPU, sometimes also called a General Purpose GPU, or GPGPU) which is an attractive proposition as a target to offload computationally demanding sections of an application running on a standard CPU.

GPUs were originally designed to display computer graphics, but they have developed into extremely powerful chips capable of handling demanding, more general-purpose calculations. The GPU architecture is somewhat different to that of the more familiar CPU. Much more space on the silicon is devoted to computation: each GPU possesses hundreds of cores of a much simpler design than a full-featured CPU. Also, GPUs use "Graphics Memory", which is much faster at loading data than the traditional memory used by CPUs; memory performance being a very important aspect for many scientific applications. These differences offer great opportunities for boosting the performance of scientific applications, but at a cost in terms of software development effort; GPUs cannot be programmed with traditional computing languages, and delicate tuning is needed to fully exploit GPUs. This is because the simple GPU cores lack the CPU's considerable logic devoted to managing outof-order execution. As a consequence, code must be tailored to fit a narrow hardware performance window, or suffer a very long execution time. This is true of many other accelerators as well, including Intel's MIC family.

A particular challenge (at least with current GPUs) is caused by accelerators having their own memory space, so the programmer must manage the memory transfers to and from the accelerator; a task that is not supported in traditional programming languages. In future products, there will probably be closer integration between CPU and GPU hardware, perhaps alleviating this issue, although it is an open guestion as to whether cache-coherency will be achievable for the CPU and GPU.

### 3.3.4 Node Level Computational Performance

The increasing performance of future systems is likely to come largely from increased performance at the node level, rather than dramatic increases in the number of nodes. In the short term we will see increasing number of CPU cores per node, possibly combined with accelerators consisting of high numbers of simpler, GPU-like cores. In the longer term we may well see closer integration, or a blurring of the distinction between CPUs and accelerators, but nevertheless each node will likely contain small numbers of sophisticated CPU cores plus high numbers on simplistic number-crunching cores. The memory per node will increase, but not at the speed of the computational increase, i.e. the memory per core will decrease.

The commonly-used method of using a separate message-passing task per core, and subsequently partitioning the memory, is unlikely to be appropriate or feasible on very high numbers of simple cores due to memory, computational and/or communication overheads. A more natural way to abstract the hardware is to use a hybrid model with small numbers of message-passing tasks on each node comprising larger numbers of some sort of lightweight threads.

## 3.4 Novel Programming Methods

## 3.4.1 Partitioned Global Address Space (PGAS) Languages

PGAS languages differ from the "traditional" models described above by introducing the concept of a global memory space that is partitioned between the participating processes (like ranks in MPI), with each process able to access both local and remote memory. Access to local memory is via standard sequential program mechanisms, and access to remote memory is directly supported by the new features of the language and is usually done in a "single-sided" manner (unlike the double-sided, matched send/receive API of, for instance, MPI). This not only enables (in principle) more productive parallel programming, it also allows the compiler to perform type checking and to optimise communications, since the compiler is aware of both the computation and communication requirements of the source. There are no penalties for local memory access. The single-sided programming model is more natural than the message-passing alternative for some algorithms, and it is also a good match for modern networks that support Remote Direct Memory Access (RDMA), potentially offering performance advantages over message-passing techniques.

#### 3.4.1.1 Co-Array Fortran

Fortran Co-Arrays are an example of a PGAS model and a relatively new mechanism for performing communications in parallel Fortran applications. The Co-Array Fortran model [8] was introduced in its current form in 1998 as a simple extension to the Fortran 95 language, and a subset of core features was formally integrated into the Fortran 2008 standard (where the spelling was changed to "coarray"). The expectation is that additional features will be published in a Technical Specification in due course. At this time, there is limited availability of Fortran implementations that support coarrays, although since they are now part of the standard the situation is expected to improve. Co-array Fortran programs follow a Single Program, Multiple Data (SPMD) model: like MPI, a single program is replicated a fixed number of times. Each replication is referred to as an "image", and images are executed asynchronously. The execution path may differ from image to image: each image has a unique identifier that can be used in control statements. A new, co-dimension syntax is used in addition to the standard array dimension syntax. For example,

#### real :: x(10)[\*]

declares a co-array that has a (standard) dimension of size 10 on each image. The square brackets define the codimension, with \* allowing the number of images to be specified when the job is launched. There is a separate copy of x on each image which can be locally accessed in the normal way (e.g. x(4) refers to the 4th element of the local x array). The co-dimension syntax allows remote memory accesses, e.g. x(4)[j] will access the fourth element of x on the jth image, which will be a remote access for all images except image j. There are a number of additional features, e.g. regarding synchronisation of images and the retrieving of information about images.

#### 3.4.1.2 Unified Parallel C

Unified Parallel C (UPC) [9] is analogous to Co-array Fortran in the sense that it extends the C programming language to provide support for explicit parallelism and the ability to access remote, as well as local, memory. However, there are differences in the way that this is done. Furthermore UPC is not part of the C standard, but instead an extension to the language. Both commercial and open source compilers are available.

Similarly to CAF, UPC is a PGAS model and programs operate in Single Program, Multiple Data (SPMD) fashion: multiple processes execute the same program, but the execution paths can differ. Whereas CAF uses the term image to refer to one process, UPC uses the term thread (noting this has a different meaning to, e.g. OpenMP threads). To allow threads to access both local and remote memory, UPC provides at the program level the concept of two memory spaces: private and shared. Objects declared in private memory space use regular C declarations, e.g.

#### int x; // private variable

and are only accessible by a single thread. Objects declared in shared memory space using the "shared" identifier, e.g.

#### shared int y; // shared variable

are accessible by all threads. The shared memory space is used to communicate information between threads. All threads can directly access shared data, even if it resides in a remote location. UPC creates a logical partitioning of the shared memory space, and shared objects have affinity to a specific thread. Shared arrays can be declared with the affinity distributed between threads (and additional syntax allows control over the specific decomposition). This affinity corresponds to physical locality: better performance will be realised when a thread accesses data to which it has affinity (i.e. it resides on the local node) compared to when it accesses data which has affinity with another thread (which resides on a node on which that thread is running). It is up to the programmer to always keep data locality and affinity in mind when designing programs that perform well.

Computation on shared distributed arrays can be shared among a set of threads. UPC has built-in mechanisms for explicitly distributing and sharing work, such as a forall loop, similar to a standard for loop in C but with the loop iterations distributed. There are a number of additional features, e.g. regarding synchronisation.

#### 3.4.1.3 OpenSHMEM

Whilst it is not exactly a PGAS language, there is increasing interest in the SHMEM communications model, which can be called from any of the traditional programming models via library API calls. SHMEM provides a SPMD execution model (like CAF and MPI), with a single-sided model of communications. The recently formed OpenSHMEM standards group [10] is currently finalising version 1.0 of an OpenSHMEM standard, unifying a number of vendor-specific variants.

#### 3.4.1.4 Interoperability

On many HPC systems there is considerable advantage in using PGAS languages. Given that CAF and UPC are extensions to existing, interoperable languages it is reasonable to expect some degree of interoperability between the parallel programming models, especially as (on a given platform) they probably share a common underlying software stack. Interoperability would allow users to incrementally port their application, assessing performance and productivity advantages as they do this. Having to completely rewrite an application in a relatively untested (at least from most users' point of view) programming model is a significant barrier to widespread adoption.

The main problem with such interoperability is that each of the languages and parallelisation models is standardised in isolation, and no standard formalises this interaction with other programming models.

In most (if not all) implementations, CAF interoperates with MPI. The image number corresponds directly with the MPI rank. This makes it simple to replace MPI send operations with CAF puts. This allows incremental porting of a Fortran MPI code, taking advantage of the PGAS features where appropriate. In practice, however, the interoperability can be complicated by the use of MPI features like subcommunicators and datatypes.

The same statements hold for the interoperability of SHMEM with MPI and with CAF. It is possible for there to be some degree of interoperability between UPC and MPI and/or SHMEM, but this is not well explored at present.

#### 3.4.1.5 Other PGAS Languages

Co-Array Fortran and UPC can be regarded as PGAS extensions to the traditional Fortran and C languages respectively. There also exist other, more radical, PGAS languages that are currently less mature and popular. Three of these emerged from the DARPA-led High Productivity Computing Systems programme: X10, Fortress and Chapel. X10 [11] is a parallel object-oriented language originally developed by IBM. The syntax is very close to Java and C++, but the language provides parallel programming concepts such as "places" which provide an abstraction of some subset of the hardware and "activities" that execute efficiently on that subset. Fortress [12], originally created by Sun Microsystems, also provides a global-view of the parallel program, and it uses the terminology of a "location" to refer to a specific memory space and the threads operating on that memory space. The Fortress syntax, though, is guite different to X10: it is an evolution of Fortran that aims to closely resemble mathematical operations, and hence be a productive tool for scientists. If developers can program using high-level mathematical concepts then underlying parallel implementation can be handled implicitly.

Chapel [13] aims to improve the programmability of parallel computers by allowing a higher level of algorithmic expression and by improving the separation of this from the details of how data is distributed across the system. A particular feature of Chapel is "multi-resolution": users initially write very abstract code and then incrementally add more detail until they are as close to the machine as their (performance) needs require.

Whilst Chapel has an imperative block structure (as in Fortran, C and C++), it currently lacks interoperability with other programming models, as do the rest of these novel languages, which is a considerable barrier to widespread uptake and exploitation.

#### 3.4.2 GPU Programming Models

Systems in which the traditional CPUs are augmented by Graphics Processing Units (GPUs) are becoming more common. The GPU acts as an "accelerator" to the CPU: most lines of application source code are executed on the CPU (using the standard serial computing model of computation) and key computational kernels are executed on the GPU (using the stream computing model of computation), taking advantage of the large number of cores and high graphics memory bandwidth on offer, with the aim that the code as a whole performs better than if the CPU was used alone. In the November 2011 edition of the Top 500 Supercomputer rankings [14], 37 of the 500 systems were of this nature. Of these, 35 contained GPUs manufactured by NVIDIA while the remaining 2 contained GPUs manufactured by AMD.

#### 3.4.2.1 NVIDIA CUDA

Compute Unified Device Architecture (CUDA) [15] is the proprietary interface to the NVIDIA architecture, and consists of extensions to C/C++ that allow interfacing to the GPU hardware. An analogous Fortran version of CUDA ("CUDA Fortran") is available as a commercial third-party product from the Portland Group compiler vendor [16].

GPUs operate under the "stream computing" model of computation, where the data set is decomposed into a stream of elements. A single computational function (or kernel) operates on each element: multiple cores can process multiple elements in parallel. This model is obviously only suitable for data-parallel problems. The NVIDIA GPU is partitioned into Streaming Multiprocessors (SMs), with multiple "CUDA cores" per SM, which operate in a vector fashion. There are less scheduling units than cores on each SM and threads are scheduled in "warps" of size 32. Threads within a warp always execute the same instruction in lock-step (on different data elements). In CUDA, this hardware is abstracted as "Grid" of "Thread Blocks". The multiple blocks in a grid map onto the multiple SMs. Each block in a grid contains multiple "threads", mapping onto the cores in an SM. CUDA extends C with the required new syntax for specifying grid/thread block decompositions, defining and launching kernels, and managing data transfers between the separate CPU and GPU memory spaces.

We illustrate by way of simple example. Consider the following sequential vector addition loop:

for (i=0:i<N:i++){ c[i] = a[i] + b[i];

3

To run this on the GPU using CUDA, we first need to use CUDA API calls to allocate memory on the GPU, and copy the a and b arrays to the GPU memory. Then we launch a kernel on the GPU:

#### vectorAdd<<<N/256, 256>>>(a, b, c);

and finally, again using API calls, copy the c array back to the CPU and free GPU memory. The <<<...>>> notation is used to define the decomposition of loop iterations over the parallel threads. Here, we have specified a 1D decomposition (where 2D and 3D decompositions are also possible), with 256 threads per block, and N/256 blocks. The vectorAdd kernel is defined as a function with the \_\_global\_\_ qualifier:

## \_\_global\_\_ void vectorAdd(float \*a\_gpu, float \*b\_gpu, float \*c\_gpu)

int i = blockldx.x \* blockDim.x + threadldx.x; c\_gpu[i] = a\_gpu[i] + b\_gpu[i]; }

where the internal variables thread/dx.x and blockId.x are unique thread/block identifiers, and blockDim.x is the number of threads per block. The kernel is therefore executed by each of the N threads, with each thread responsible for a single element of the vector.

As this example demonstrates, CUDA is very powerful in providing functionality to flexibly utilise the GPU hardware, but has the serious caveat that the resulting code is much more complex than the equivalent CPU code.

#### 3.4.2.2 OpenCL

Open Compute Language (OpenCL) [17] is a cross-platform API that can be used to program not just GPU-accelerated systems, but also other heterogeneous and/or multicore architectures. When used to program GPU accelerated systems, the model is very similar to that of CUDA. There are similar abstractions and basic functionality, with differing terminology, e.g. a "Thread" in CUDA is expressed as a "Work Item" in OpenCL. The key advantage of OpenCL over CUDA is that it is portable to other systems, such as those utilising AMD GPUs, although adaptations still may be required for performance. At this point in time CUDA remains more mature and well documented for use on NVIDIA systems. OpenCL addresses the hardware at a slightly lower level, resulting in more work for the programmer. For example, OpenCL does not add any new language syntax so the launching of each kernel involves a series of library calls; in CUDA this is hidden from the user by use of the <<<...>>> syntax (see the previous section).

#### 3.4.2.3 Accelerator Directives

Directive-based programming of GPUs and other accelerating co-processors is a relatively new, high-level programming model that provides an alternative to rewriting applications in GPU-specific languages (such as CUDA or OpenCL). As has been discussed above, the vast majority of large-scale, parallel scientific codes are written in the traditional HPC languages Fortran, C and C++. Many of the algorithms used are, or can be made to be, extremely suitable for running on the vector-like architectures of GPUs. Rather than rewriting, a better approach (from a developer productivity viewpoint) is to provide a mechanism for compilers to generate executables that can run on the GPU from the original source code.

Most accelerators have a radically different architecture to a typical CPU. In particular, they have a narrow performance range, and kernels with the wrong loop structure or pattern of memory access will run with extremely low efficiency. It is unlikely, then, that any compiler would be able to automatically generate efficient executables for the accelerator without guidance from the application developer. Accelerator directives provide a mechanism for the developer to add such guidance for the compiler, by means of non-executable statements (specially-constructed comments) in the code. A non-accelerating compiler that targets a CPU would ignore these, but an accelerating compiler can interpret these as prescriptive or suggestive information that control the creation of kernels that will execute on the accelerator.

Directive-based programming models are not new and OpenMP provides a good example that such models can be successful, both in terms of allowing the compiler to generate efficient code and in being widely adopted by the user communities.

The first widely available accelerator directive programming models were vendor-specific, from PGI [18] and CAPS [19]. Whilst these both have some use, widespread uptake requires vendors to feel that the programming model(s) have some permanency via an external standardisation process. There are currently two such efforts on-going.

The first is via the established OpenMP Architecture Review Board (ARB) standards committee [3]. A subcommittee was established to develop an extension to the existing OpenMP 3.0 standard that would target a wide class of possible accelerators. This would include GPUs, but also address other accelerators e.g. digital signal processors (DSPs). The work of this committee is on going, with a draft standard being discussed in weekly or biweekly conference calls. The basis for this draft standard was the PGI directive model, but almost all large-scale compiler vendors are represented.

More recently, it was recognised that while the OpenMP specification evolved, there was a need for a minimal, interim standard to serve early adopters of the directive-programming model. This would provide a published document describing the model (as opposed to the fluid draft OpenMP proposal) and would allow portability of code between multiple compiler vendors.

To this end, the OpenACC standard [20] launched in November 2011, with support from NVIDIA (as GPU hardware manufacturer) and compiler developers Cray, PGI and CAPS.

For most simple examples, the differences between all these programming models are largely semantic. By way of example, we focus on using OpenACC directives to accelerate a two-dimensional stencil calculation followed by calculation of a residual (ignoring the fact that really only one loopnest is required for this simplistic example):

```

!$acc data copyin(b) copyout(a)

!$acc parallel loop

DO i = 2,N-1

DO j = 2,M-1

a(i,j) = b(i+1,j) + b(i-1,j) + b(i,j+1) + b(i,j-1)

ENDDO

ENDDO

!$acc end parallel loop

residual = 0

!$acc parallel loop reduction(+:residual)

DO i = 2,N-1

DO j = 2,M-1

residual = residual + a(i,j)

ENDDO

ENDDO

!$acc end parallel loop

Sacc end data

```

Each loopnest is compiled as a kernel on the accelerator. The compiler chooses a default loop schedule (division of loop iterations across the computational cores of the accelerator). Optional clauses on the directives can be used to influence this choice. As in traditional OpenMP, reduction variables are identified using an appropriate clause.

Given the separate memory spaces of the CPU and GPU, good performance can only be gained by minimising data transfers. The enclosing data region instructs the compiler to minimise data traffic by only moving the data arrays before or after the two kernels (rather than for each one), and movements are tuned to match the read-only and write-only use of the arrays in the loopnests. If a variable (scalar or array) is not mentioned in a data region, data movement occurs at the boundaries of the parallel loop region.

With this level of control, the compiler has the potential to deliver code that performs well on the GPU as well as on the CPU. The developers of the Cray compiler, for instance, expect accelerator directivegenerated code to typically deliver 90% or more of the performance of an equivalent code handwritten in CUDA.

Being based on the original source code, interoperability of the generated kernels with the host, CPU code is assured. More importantly, there is increasing work to support interoperability of the directive-based model with more established GPU-targeted programming models like CUDA.

# 4 COMPILATION AND RUNTIME ENVIRONMENTS

## 4.1 Compilers for Exascale Computing

The fundamental job of a serial compiler is to take the programmer's high-level, generic, humanreadable source-code description of some algorithm or operation and translate it into low-level machine code that is specific to a particular CPU architecture. In order to be as general-purpose as possible, modern compilers defer the architecture-specific aspects to a very late stage, performing code transformations using some architecture-neutral intermediate representation of the source code. Compilers also deal with multiple high-level languages by converting all of them to the same intermediate representation.

Modern compilers are all generally good at improving code performance through "classical" optimisation techniques such as removal of redundant code, storing temporary values in registers rather than memory, function inlining, loop unrolling etc. However, the ever increasing gap between the rate at which CPUs can issue instructions and the speed of DRAM means that the limiting factor in many codes is the way in which data is read from and written to memory, rather than the rate at which floating-point instructions are issued. This means that the most important optimisations concern how user data is laid out in memory and how it is accessed within loops.

Most compilers can already address some of these issues. For nested loops, the loop ordering may be changed so that memory access is done efficiently (e.g. to match Fortran row-major array storage order). Loops may be split into many separate chunks (a technique called "tiling") to improve data reuse and make better use of the CPU's caches. Prefetching may be inserted to load data from memory well before it is required to try and hide memory latencies. However, all these classical techniques suffer from three major limitations.

Firstly, the executable is generated based purely on the information in the source code. In reality the optimal set of loop transformations depends critically on the dimensions of the arrays being processed and the extents of the loops being executed. In many cases these are not known at compile time and will depend on the data set. Since a single application is typically run against multiple data sets this implies that separate executables may be required for different runs of the same code. It is possible to generate a single executable containing multiple versions of a routine and choose the most appropriate one at runtime based on the specific input parameters. However, this technique cannot cope with the huge number of possible options for real codes.

Secondly, the compiler is optimising against some theoretical model of the CPU architecture, e.g. it may assume that a certain amount of cache is available per core and tile the loops to fit this size. This may have been effective in the past with simple memory architectures, but modern multicore processors are becoming so complicated that it is almost impossible to make accurate predictions about achieved performance from simple theoretical models.